Deeds - DMC8 Processor

(Instruction Set)

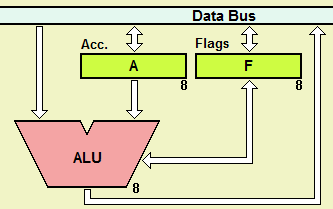

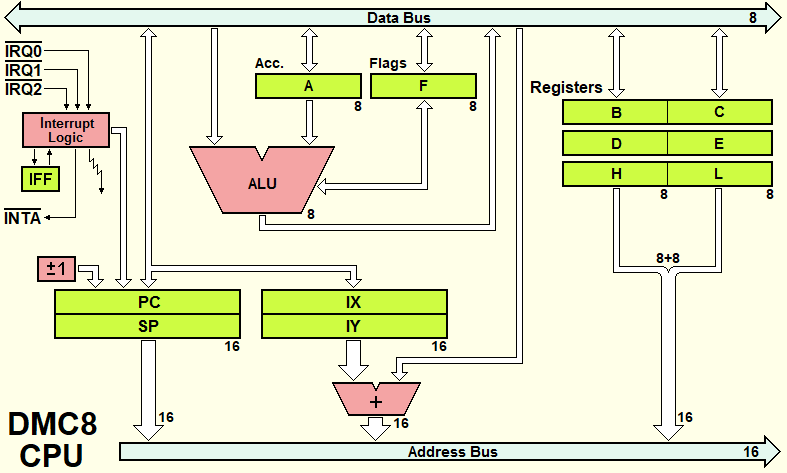

DMC8 Processor Programming Model

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

|

| LD r, r |

r r |

|

01 r r |

1 |

1 |

4 |

r,

r Reg |

||

| LD r, n |

r n |

|

00 r 110 |

2 |

2 |

7 |

|||

| LD r, (HL) |

r (HL) |

|

01 r 110 |

1 |

2 |

7 |

|||

| LD r, (IX + d) |

r (IX + d) |

|

11 011 101 |

DD |

3 |

5 |

19 |

||

| LD r, (IY + d) |

r (IY + d) |

|

11 111 101 |

FD |

3 |

5 |

19 |

||

| LD (HL), r |

(HL) r |

|

01 110 r |

1 |

2 |

7 |

|||

| LD (IX + d), r |

(IX + d) r |

|

11 011 101 |

DD |

3 |

5 |

19 |

||

| LD (IY + d), r |

(IY + d) r |

|

11 111 101 |

FD |

3 |

5 |

19 |

||

| LD (HL), n |

(HL) n |

|

00 110 110 |

36 |

2 |

3 |

10 |

||

| LD (IX + d), n |

(IX + d) n |

|

11 011 101 |

DD |

4 |

5 |

19 |

||

| LD (IY + d), n |

(IY + d) n |

|

11 111 101 |

FD |

4 |

5 |

19 |

||

| LD A, (BC) |

A (BC) |

|

00 001 010 |

0A |

1 |

2 |

7 |

||

| LD A, (DE) |

A (DE) |

|

00 011 010 |

1A |

1 |

2 |

7 |

||

| LD A, (nn) |

A (nn) |

|

00 111 010 |

3A |

3 |

4 |

13 |

||

| LD (BC), A |

(BC) A |

|

00 000 010 |

02 |

1 |

2 |

7 |

||

| LD (DE), A |

(DE) A |

|

00 010 010 |

12 |

1 |

2 |

7 |

||

| LD (nn), A |

(nn) A |

|

00 110 010 |

32 |

3 |

4 |

13 |

||

| Notes: |

r, r means any of the registers A, B, C, D, E, H, L. |

||||||||

| Flag Notation: |

= flag is not affected. |

||||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

|

| LD dd, nn |

dd ¬ nn |

• • • • • • |

00 dd0 001 |

3 |

3 |

10 |

dd Pair |

||

| LD IX, nn |

IX ¬ nn |

• • • • • • |

11

011 101 |

DD |

4 |

4 |

14 |

||

| LD IY, nn |

IY ¬ nn |

• • • • • • |

11 111 101 |

FD |

4 |

4 |

14 |

||

| LD HL, (nn) |

L ¬ (nn) |

• • • • • • |

00 101 010 |

2A |

3 |

5 |

16 |

||

| LD dd, (nn) |

ddL ¬ (nn) |

• • • • • • |

11 101 101 |

ED |

4 |

6 |

20 |

||

| LD IX, (nn) |

IXL ¬ (nn) |

• • • • • • |

11 011 101 |

DD |

4 |

6 |

20 |

||

| LD IY, (nn) |

IYL ¬

(nn) |

• • • • • • |

11 111 101 |

FD |

4 |

6 |

20 |

||

| LD (nn), HL |

(nn) ¬ L |

• • • • • • |

00 100 010 |

22 |

3 |

5 |

16 |

||

| LD (nn), dd |

(nn) ¬ ddL |

• • • • • • |

11 101 101 |

DD |

4 |

6 |

20 |

||

| LD (nn), IX |

(nn) ¬ IXL |

• • • • • • |

11 011 101 |

DD |

4 |

6 |

20 |

||

| LD (nn), IY |

(nn) ¬ IYL |

• • • • • • |

11 111 101 |

FD |

4 |

6 |

20 |

||

| LD SP, HL |

SP ¬ HL |

• • • • • • |

11 111 001 |

F9 |

1 |

1 |

6 |

||

| LD SP, IX |

SP ¬ IX |

• • • • • • |

11 011 101 |

DD |

2 |

2 |

10 |

||

| LD SP, IY |

SP ¬ IY |

• • • • • • |

11 111 101 |

FD |

2 |

2 |

10 |

||

| EX DE,HL |

DE « HL |

• • • • • • |

11 101 011 |

EB |

1 |

1 |

4 |

||

| EX (SP), HL |

H « (SP+1) |

• • • • • • |

11 100 011 |

E3 |

1 |

5 |

19 |

||

| PUSH qq |

SP ¬ SP - 1 |

• • • • • • |

11 qq0 101 |

1 |

3 |

11 |

qq Pair |

||

| PUSH IX |

SP ¬ SP - 1 |

• • • • • • |

11 011 101 |

DD |

2 |

4 |

15 |

||

| PUSH IY |

SP ¬ SP - 1 |

• • • • • • |

11 111 101 |

FD |

2 |

4 |

15 |

||

| POP qq |

qqL ¬ (SP) |

• • • • • • |

11 qq0 001 |

1 |

3 |

10 |

|||

| POP IX |

IXL ¬ (SP) |

• • • • • • |

11 011 101 |

DD |

2 |

4 |

14 |

||

| POP IY |

IYL ¬ (SP) |

• • • • • • |

11 111 101 |

FD |

2 |

4 |

14 |

||

| Notes: |

dd is any of the register pair BC, DE, HL, SP. |

||||||||

| Flag Notation: |

• = flag is not affected. |

||||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| ADD A, r |

A ¬ A + r |

↕ ↕ ↕ V 0 ↕ |

10 000 r |

1 |

1 |

4 |

r Reg |

|

| ADD A, n |

A ¬ A + n |

↕ ↕ ↕ V 0 ↕ |

11 000 110 |

2 |

2 |

7 |

||

| ADD A, (HL) |

A ¬ A + (HL) |

↕ ↕ ↕ V 0 ↕ |

10 000 110 |

1 |

2 |

7 |

||

| ADD A, (IX + d) |

A ¬ A + (IX + d) |

↕ ↕ ↕ V 0 ↕ |

11 011 101 |

DD |

3 |

5 |

19 |

|

| ADD A, (IY + d) |

A ¬ A + (IY + d) |

↕ ↕ ↕ V 0 ↕ |

11 111 101 |

FD |

3 |

5 |

19 |

|

ADC A, r |

A ¬ A + r + CY |

↕ ↕ ↕ V 0 ↕ |

10 001 r |

1 |

1 |

4 |

||

ADC A, n |

A ¬ A + n + CY |

↕ ↕ ↕ V 0 ↕ |

11 001 110 |

2 |

2 |

7 |

||

ADC A, (HL) |

A ¬ A + (HL) + CY |

↕ ↕ ↕ V 0 ↕ |

10 001 110 |

1 |

2 |

7 |

||

ADC A, (IX + d) |

A ¬ A + (IX + d) + CY |

↕ ↕ ↕ V 0 ↕ |

11 011 101 |

DD |

3 |

5 |

19 |

|

ADC A, (IY + d) |

A ¬ A + (IY + d) + CY |

↕ ↕ ↕ V 0 ↕ |

11 111 101 |

FD |

3 |

5 |

19 |

|

| SUB r |

A ¬ A - r |

↕ ↕ ↕ V 1 ↕ |

10 010 r |

1 |

1 |

4 |

||

| SUB n |

A ¬ A - n |

↕ ↕ ↕ V 1 ↕ |

11 010 110 |

2 |

2 |

7 |

||

| SUB (HL) |

A ¬ A - (HL) |

↕ ↕ ↕ V 1 ↕ |

10 010 110 |

1 |

2 |

7 |

||

| SUB (IX + d) |

A ¬ A - (IX + d) |

↕ ↕ ↕ V 1 ↕ |

11 011 101 |

DD |

3 |

5 |

19 |

|

| SUB (IY + d) |

A ¬ A - (IY + d) |

↕ ↕ ↕ V 1 ↕ |

11 111 101 |

FD |

3 |

5 |

19 |

|

SBC A, r |

A ¬ A - r - CY |

↕ ↕ ↕ V 1 ↕ |

10 011 r |

1 |

1 |

4 |

||

SBC A, n |

A ¬ A - n - CY |

↕ ↕ ↕ V 1 ↕ |

11 011 110 |

2 |

2 |

7 |

||

SBC A, (HL) |

A ¬ A - (HL) - CY |

↕ ↕ ↕ V 1 ↕ |

10 011 110 |

1 |

2 |

7 |

||

SBC A, (IX + d) |

A ¬ A - (IX + d) - CY |

↕ ↕ ↕ V 1 ↕ |

11 011 101 |

DD |

3 |

5 |

19 |

|

SBC A, (IY + d) |

A ¬ A - (IY + d) - CY |

↕ ↕ ↕ V 1 ↕ |

11 111 101 |

FD |

3 |

5 |

19 |

|

| CP r |

A - r |

↕ ↕ ↕ V 1 ↕ |

10 111 r |

1 |

1 |

4 |

||

| CP n |

A - n |

↕ ↕ ↕ V 1 ↕ |

11 111 110 |

2 |

2 |

7 |

||

| CP (HL) |

A - (HL) |

↕ ↕ ↕ V 1 ↕ |

10 111 110 |

1 |

2 |

7 |

||

| CP (IX + d) |

A - (IX + d) |

↕ ↕ ↕ V 1 ↕ |

11 011 101 |

DD |

3 |

5 |

19 |

|

| CP (IY + d) |

A - (IY + d) |

↕ ↕ ↕ V 1 ↕ |

11 111 101 |

FD |

3 |

5 |

19 |

|

AND r |

A ¬ A and r |

↕ ↕ 1 P 0 0 |

10 100 r |

1 |

1 |

4 |

||

AND n |

A ¬ A and n |

↕ ↕ 1 P 0 0 |

11 100 110 |

2 |

2 |

7 |

||

AND (HL) |

A ¬ A and (HL) |

↕ ↕ 1 P 0 0 |

10 100 110 |

1 |

2 |

7 |

||

AND (IX + d) |

A ¬ A and (IX + d) |

↕ ↕ 1 P 0 0 |

11 011 101 |

DD |

3 |

5 |

19 |

|

AND (IY + d) |

A ¬ A and (IY + d) |

↕ ↕ 1 P 0 0 |

11 111 101 |

FD |

3 |

5 |

19 |

|

OR r |

A ¬ A or r |

↕ ↕ 1 P 0 0 |

10 110 r |

1 |

1 |

4 |

||

OR n |

A ¬ A or n |

↕ ↕ 1 P 0 0 |

11 110 110 |

2 |

2 |

7 |

||

OR (HL) |

A ¬ A or (HL) |

↕ ↕ 1 P 0 0 |

10 110 110 |

1 |

2 |

7 |

||

OR (IX + d) |

A ¬ A or (IX + d) |

↕ ↕ 1 P 0 0 |

11 011 101 |

DD |

3 |

5 |

19 |

|

OR (IY + d) |

A ¬ A or (IY + d) |

↕ ↕ 1 P 0 0 |

11 111 101 |

FD |

3 |

5 |

19 |

|

XOR r |

A ¬ A xor r |

↕ ↕ 1 P 0 0 |

10 101 r |

1 |

1 |

4 |

||

XOR n |

A ¬ A xor n |

↕ ↕ 1 P 0 0 |

11 101 110 |

2 |

2 |

7 |

||

XOR (HL) |

A ¬ A xor (HL) |

↕ ↕ 1 P 0 0 |

10 101 110 |

1 |

2 |

7 |

||

XOR (IX + d) |

A ¬ A xor (IX + d) |

↕ ↕ 1 P 0 0 |

11 011 101 |

DD |

3 |

5 |

19 |

|

XOR (IY + d) |

A ¬ A xor (IY + d) |

↕ ↕ 1 P 0 0 |

11 111 101 |

FD |

3 |

5 |

19 |

|

| INC r |

r ¬ r + 1 |

↕ ↕ ↕ V 0 • |

00 r 100 |

1 |

1 |

4 |

||

| INC (HL) |

(HL) ¬ (HL) + 1 |

↕ ↕ ↕ V 0 • |

00 110 100 |

1 |

3 |

11 |

||

| INC (IX + d) |

(IX + d) ¬ (IX + d) + 1 |

↕ ↕ ↕ V 0 • |

11 011 101 |

DD |

3 |

6 |

23 |

|

| INC (IY + d) |

(IY + d) ¬ (IY + d) + 1 |

↕ ↕ ↕ V 0 • |

11 111 101 |

FD |

3 |

6 |

23 |

|

| DEC r |

r ¬ r - 1 |

↕ ↕ ↕ V 1 • |

00 r 101 |

1 |

1 |

4 |

||

| DEC (HL) |

(HL) ¬ (HL) - 1 |

↕ ↕ ↕ V 1 • |

00 110 101 |

1 |

3 |

11 |

||

| DEC (IX + d) |

(IX + d) ¬ (IX + d) -1 |

↕ ↕ ↕ V 1 • |

11 011 101 |

DD |

3 |

6 |

23 |

|

| DEC (IY + d) |

(IY + d) ¬ (IY + d) - 1 |

↕ ↕ ↕ V 1 • |

11 111 101 |

FD |

3 |

6 |

23 |

|

| DAA |

Converts Accumulator contents into packed BCD, following add or subtract with packed BCD operands |

↕ ↕ ↕ P • ↕ | 00 100 111 |

27 |

1 |

1 |

4 |

|

| CPL |

_ |

• • 1 • 1 • |

00 101 111 |

2F |

1 |

1 |

4 |

One’s complement. |

| NEG |

_ |

↕ ↕ ↕ V 1 ↕ |

11 101 101 |

ED |

2 |

2 |

8 |

Two’s complement. |

| Notes: |

The V symbol in the P/V flag column indicates that the P/V

flag contains the overflow of the operation. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| ADD HL, ss |

HL ¬ HL + ss |

• • ↕2 • 0 ↕1 |

00 ss1 001 |

1 |

3 |

11 |

ss Reg. pp Reg. rr Reg. |

|

| ADC HL, ss |

HL ¬ HL + ss + CY |

↕1 ↕1 ↕2 V1 0 ↕1 |

11 101 101 |

ED |

2 |

4 |

15 |

|

| SBC HL, ss |

HL ¬ HL – ss – CY |

↕1 ↕1 ↕2 V1 1 ↕1 |

11 101 101 |

ED |

2 |

4 |

15 |

|

| ADD IX, pp |

IX ¬ IX + pp |

• • ↕2 • 0 ↕1 |

11 011 101 |

DD |

2 |

4 |

15 |

|

| ADD IY, rr |

IY ¬ IY + rr |

• • ↕2 • 0 ↕1 |

11 111 101 |

FD |

2 |

4 |

15 |

|

| INC ss |

ss ¬ ss + 1 |

• • • • • • |

00 ss0 011 |

1 |

1 |

6 |

||

| INC IX |

IX ¬ IX + 1 |

• • • • • • |

11 011 101 |

DD |

2 |

2 |

10 |

|

| INC IY |

IY ¬ IY + 1 |

• • • • • • |

11 111 101 |

FD |

2 |

2 |

10 |

|

| DEC ss |

ss ¬ ss - 1 |

• • • • • • |

00 ss1 011 |

1 |

1 |

6 |

||

| DEC IX |

IX ¬ IX - 1 |

• • • • • • |

11 011 101 |

DD |

2 |

2 |

10 |

|

| DEC IY |

IY ¬ IY - 1 |

• • • • • • |

11 111 101 |

FD |

2 |

2 |

10 |

|

| Notes: |

The V symbol in the P/V flag column indicates that the P/V

flag contains the overflow of the operation. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

|

|

___ |

• • X • 0 ↕ |

00 111 111 |

3F |

1 |

1 |

4 |

Complement |

| SCF |

CY ¬ 1 |

• • 0 • 0 1 |

00 110 111 |

37 |

1 |

1 |

4 |

|

| NOP |

No Operation |

• • • • • • |

00 000 000 |

00 |

1 |

1 |

4 |

|

| HALT |

CPU halted |

• • • • • • |

01 110 110 |

76 |

1 |

1 |

4 |

|

| DI1 |

IFF ¬ 0 |

• • • • • • |

11 110 011 |

F3 |

1 |

1 |

4 |

|

| EI1 |

IFF ¬ 1 |

• • • • • • |

11 111 011 |

FB |

1 |

1 |

4 |

|

| Notes: |

The V symbol in the P/V flag column indicates that the P/V

flag contains the overflow of the operation. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, X = flag is “unknown”, |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| JP nn |

PC ¬ nn |

• • • • • • |

11 000 011 |

C3 |

3 |

3 |

10 |

|

| JP cc, nn |

if cc is true, |

• • • • • • |

11 cc 010 |

3 |

3 |

10 |

cc Condition |

|

| JP ( HL ) |

PC ¬ HL |

• • • • • • |

11 101 001 |

E9 |

1 |

1 |

4 |

|

| JP ( IX ) |

PC ¬ IX |

• • • • • • |

11 011 101 |

DD |

2 |

2 |

8 |

|

| JP ( IY ) |

PC ¬ IY |

• • • • • • |

11 111 101 |

FD |

2 |

2 |

8 |

|

| Flag Notation: |

• = flag is not affected. |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| CALL nn |

SP ¬ SP - 1 |

• • • • • • |

11 001 101 |

CD |

3 |

5 |

17 |

|

| CALL cc, nn |

if cc is true, |

• • • • • • |

11 cc 100 |

3 |

3 |

10 |

if cc is false cc Condition |

|

| RET |

PCL ¬

(SP) |

• • • • • • |

11 001 001 |

C9 |

1 |

3 |

10 |

|

| RET cc |

if cc is true, |

• • • • • • |

11 cc 000 |

1 |

1 |

5 |

if cc is false |

|

| RST p |

SP ¬ SP - 1 |

• • • • • • |

11 t 111 |

1 |

3 |

11 |

_t_ __p__ |

|

| Flag Notation: |

• = flag is not affected. |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| RLCA |

|

• • 0 • 0 ↕ |

00 000 111 |

07 |

1 |

1 |

4 |

|

| RLA |

|

• • 0 • 0 ↕ |

00 010 111 |

17 |

1 |

1 |

4 |

|

| RRCA |

|

• • 0 • 0 ↕ |

00 001 111 |

0F |

1 |

1 |

4 |

|

| RRA |

|

• • 0 • 0 ↕ |

00 011 111 |

1F |

1 |

1 |

4 |

|

| RLC r |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

2 |

8 |

r Reg |

| RLC (HL) |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

4 |

15 |

|

| RLC (IX + d) |

|

↕ ↕ 0 P 0 ↕ |

11 011 101 |

DD |

4 |

6 |

23 |

|

| RLC (IY + d) |

|

↕ ↕ 0 P 0 ↕ |

11 111 101 |

FD |

4 |

6 |

23 |

|

| RL r |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

2 |

8 |

|

| RL (HL) |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

4 |

15 |

|

| RL (IX + d) |

|

↕ ↕ 0 P 0 ↕ |

11 011 101 |

DD |

4 |

6 |

23 |

|

| RL (IY + d) |

|

↕ ↕ 0 P 0 ↕ |

11 111 101 |

FD |

4 |

6 |

23 |

|

| RRC r |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

2 |

8 |

|

| RRC (HL) |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

4 |

15 |

|

| RRC (IX + d) |

|

↕ ↕ 0 P 0 ↕ |

11 011 101 |

DD |

4 |

6 |

23 |

|

| RRC (IY + d) |

|

↕ ↕ 0 P 0 ↕ |

11 111 101 |

FD |

4 |

6 |

23 |

|

| RR r |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

2 |

8 |

|

| RR (HL) |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

4 |

15 |

|

| RR (IX + d) |

|

↕ ↕ 0 P 0 ↕ |

11 011 101 |

DD |

4 |

6 |

23 |

|

| RR (IY + d) |

|

↕ ↕ 0 P 0 ↕ |

11 111 101 |

FD |

4 |

6 |

23 |

|

| RLD |

|

↕ ↕ 0 P 0 • |

11 101 101 |

ED |

2 |

5 |

18 |

|

| RRD |

|

↕ ↕ 0 P 0 • |

11 101 101 |

ED |

2 |

5 |

18 |

|

| SLA r |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

2 |

8 |

r Reg |

| SLA (HL) |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

4 |

15 |

|

| SLA (IX + d) |

|

↕ ↕ 0 P 0 ↕ |

11 011 101 |

DD |

4 |

6 |

23 |

|

| SLA (IY + d) |

|

↕ ↕ 0 P 0 ↕ |

11 111 101 |

FD |

4 |

6 |

23 |

|

| SRA r |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

2 |

8 |

|

| SRA (HL) |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

4 |

15 |

|

| SRA (IX + d) |

|

↕ ↕ 0 P 0 ↕ |

11 011 101 |

DD |

4 |

6 |

23 |

|

| SRA (IY + d) |

|

↕ ↕ 0 P 0 ↕ |

11 111 101 |

FD |

4 |

6 |

23 |

|

| SRL r |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

2 |

8 |

|

| SRL (HL) |

|

↕ ↕ 0 P 0 ↕ |

11 001 011 |

CB |

2 |

4 |

15 |

|

| SRL (IX + d) |

|

↕ ↕ 0 P 0 ↕ |

11 011 101 |

DD |

4 |

6 |

23 |

|

| SRL (IY + d) |

|

↕ ↕ 0 P 0 ↕ |

11 111 101 |

FD |

4 |

6 |

23 |

|

| Notes: |

The P symbol in the P/V flag column indicates that the P/V

flag contains the parity of the result. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

|

|

__ |

X ↕ 1 X 0 • |

11 001 011 |

CB |

2 |

2 |

8 |

r Reg

b Bit

|

| BIT b, (HL) |

____ |

X ↕ 1 X 0 • |

11 001 011 |

CB |

2 |

3 |

12 |

|

| BIT b, (IX + d) |

______ |

X ↕ 1 X 0 • |

11 011 101 |

DD |

4 |

5 |

20 |

|

| BIT b, (IY + d) |

______ |

X ↕ 1 X 0 • |

11 111 101 |

FD |

4 |

5 |

20 |

|

| SET b, r |

rb ¬ 1 |

• • • • • • |

11 001 011 |

CB |

2 |

2 |

8 |

|

| SET b, (HL) |

(HL)b ¬ 1 |

• • • • • • |

11 001 011 |

CB |

2 |

4 |

15 |

|

| SET b, (IX + d) |

(IX+ d)b ¬ 1 |

• • • • • • |

11 011 101 |

DD |

4 |

6 |

23 |

|

| SET b, (IY + d) |

(IY+ d)b ¬ 1 |

• • • • • • |

11 111 101 |

FD |

4 |

6 |

23 |

|

| RES b, r |

rb ¬ 0 |

• • • • • • |

11 001 011 |

CB |

2 |

2 |

8 |

|

| RES b, (HL) |

(HL)b ¬ 0 |

• • • • • • |

11 001 011 |

CB |

2 |

4 |

15 |

|

| RES b, (IX + d) |

(IX+ d)b ¬ 0 |

• • • • • • |

11 011 101 |

DD |

4 |

6 |

23 |

|

| RES b, (IY + d) |

(IY+ d)b ¬ 0 |

• • • • • • |

11 111 101 |

FD |

4 |

6 |

23 |

|

| Notes: |

The notation mb indicates bit b (0 to 7) of location

m. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, X = flag is “don’t care”, |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| IN A, (n) |

A ¬ (n) |

• • • • • • |

11 011 011 |

DB |

2 |

3 |

11 |

r Reg |

| IN r, (C) |

r ¬ (C) |

↕ ↕ 0 P 0 • |

11 101 101 |

ED |

2 |

3 |

12 |

|

| OUT (n), A |

(n) ¬ A |

• • • • • • |

11 010 011 |

D3 |

2 |

3 |

11 |

|

| OUT (C), r |

(C) ¬ r |

• • • • • • |

11 101 101 |

ED |

2 |

3 |

12 |

|

| Notes: |

The V symbol in the P/V flag column indicates that the P/V

flag contains the overflow of the operation. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, |

|||||||