Deeds - D8080 Processor

(Instruction Set)

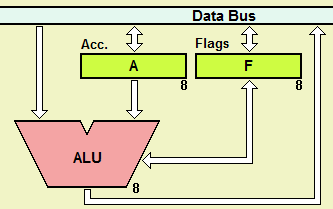

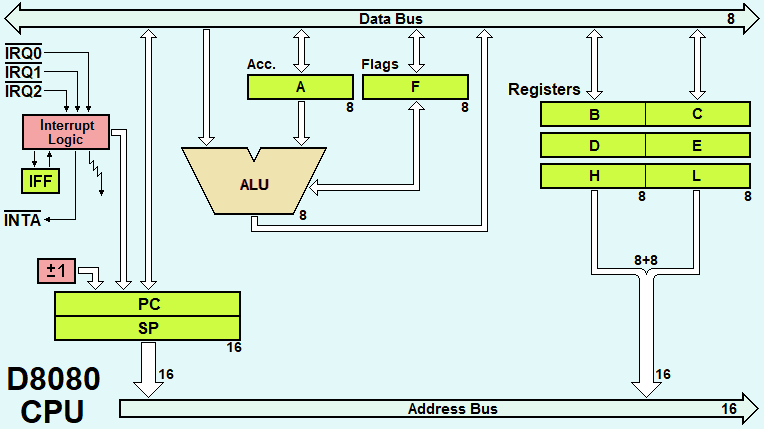

D8080 Processor Programming Model

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

|

| MOV r, r’ |

r ¬ r’ |

• • • • • |

01 r r’ |

1 |

1 |

4 |

r,

r’ Reg |

||

| MVI r, n |

r ¬ n |

• • • • • |

00 r 110 |

2 |

2 |

7 |

|||

| MOV r,M |

r ¬ (HL) |

• • • • • |

01 r 110 |

1 |

2 |

7 |

|||

| MOV M, r |

(HL) ¬ r |

• • • • • |

01 110 r |

1 |

2 |

7 |

|||

| MVI M, n |

(HL) ¬ n |

• • • • • |

00 110 110 |

36 |

2 |

3 |

10 |

||

| LDAX B |

A ¬ (BC) |

• • • • • |

00 001 010 |

0A |

1 |

2 |

7 |

||

| LDAX D |

A ¬ (DE) |

• • • • • |

00 011 010 |

1A |

1 |

2 |

7 |

||

| LDA nn |

A ¬ (nn) |

• • • • • |

00 111 010 |

3A |

3 |

4 |

13 |

||

| STAX B |

(BC) ¬ A |

• • • • • |

00 000 010 |

02 |

1 |

2 |

7 |

||

| STAX D |

(DE) ¬ A |

• • • • • |

00 010 010 |

12 |

1 |

2 |

7 |

||

| STA nn |

(nn) ¬ A |

• • • • • |

00 110 010 |

32 |

3 |

4 |

13 |

||

| Notes: |

r, r’ means any of the registers A, B, C, D, E, H, L. |

||||||||

| Flag Notation: |

• = flag is not affected. |

||||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

|

| LXI B, nn |

BC ¬ nn |

• • • • • |

00 000 001 |

01 | 3 |

3 |

10 |

|

|

| LXI D, nn |

DE ¬ nn |

• • • • • |

00 010 001 |

11 | 3 |

3 |

10 |

||

| LXI H, nn |

HL ¬ nn |

• • • • • |

00 100 001 |

21 | 3 |

3 |

10 |

||

| LXI SP, nn |

SP ¬ nn |

• • • • • |

00 110 001 |

31 | 3 |

3 |

10 |

||

| LHLD nn |

L ¬ (nn) |

• • • • • |

00 101 010 |

2A |

3 |

5 |

16 |

||

| SHLD nn |

(nn) ¬ L |

• • • • • |

00 100 010 |

22 |

3 |

5 |

16 |

||

| SPHL |

SP ¬ HL |

• • • • • |

11 111 001 |

F9 |

1 |

1 |

6 |

||

| XCHG |

DE « HL |

• • • • • |

11 101 011 |

EB |

1 |

1 |

4 |

||

| XTHL |

H « (SP+1) |

• • • • • |

11 100 011 |

E3 |

1 |

5 |

19 |

||

| PUSH B |

SP ¬ SP - 1 |

• • • • • |

11 000 101 |

C5 | 1 |

3 |

11 | ||

| PUSH D |

SP ¬ SP - 1 |

• • • • • |

11 010 101 |

D5 | 1 |

3 |

11 | ||

| PUSH H |

SP ¬ SP - 1 |

• • • • • |

11 100 101 |

E5 | 1 |

3 |

11 |

||

| PUSH PSW |

SP ¬ SP - 1 |

• • • • • |

11 110 101 |

F5 | 1 |

3 |

11 | ||

| POP B |

C ¬ (SP) |

• • • • • |

11 000 001 |

C1 | 1 |

3 |

10 | ||

| POP D |

E ¬ (SP) |

• • • • • |

11 010 001 |

D1 | 1 |

3 |

10 |

||

| POP H |

L ¬ (SP) |

• • • • • |

11 100 001 |

E1 | 1 |

3 |

10 | ||

| POP PSW |

Flags ¬ (SP) |

• • • • • |

11 110 001 |

F1 | 1 |

3 |

10 | ||

| Flag Notation: |

• = flag is not affected. |

||||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| ADD r |

A ¬ A + r |

↕ ↕ ↕ ↕ ↕ |

10 000 r |

1 |

1 |

4 |

r Reg |

|

| ADI n |

A ¬ A + n |

↕ ↕ ↕ ↕ ↕ |

11 000 110 |

2 |

2 |

7 |

||

| ADD M |

A ¬ A + (HL) |

↕ ↕ ↕ ↕ ↕ |

10 000 110 |

86 | 1 |

2 |

7 |

|

ADC r |

A ¬ A + r + CY |

↕ ↕ ↕ ↕ ↕ |

10 001 r |

1 |

1 |

4 |

||

ACI n |

A ¬ A + n + CY |

↕ ↕ ↕ ↕ ↕ |

11 001 110 |

2 |

2 |

7 |

||

ADC M |

A ¬ A + (HL) + CY |

↕ ↕ ↕ ↕ ↕ |

10 001 110 |

8E | 1 |

2 |

7 |

|

| SUB r |

A ¬ A - r |

↕ ↕ ↕ ↕ ↕ |

10 010 r |

1 |

1 |

4 |

||

| SUI n |

A ¬ A - n |

↕ ↕ ↕ ↕ ↕ |

11 010 110 |

2 |

2 |

7 |

||

| SUB M |

A ¬ A - (HL) |

↕ ↕ ↕ ↕ ↕ |

10 010 110 |

96 | 1 |

2 |

7 |

|

SBB r |

A ¬ A - r - CY |

↕ ↕ ↕ ↕ ↕ |

10 011 r |

1 |

1 |

4 |

||

SBI n |

A ¬ A - n - CY |

↕ ↕ ↕ ↕ ↕ |

11 011 110 |

2 |

2 |

7 |

||

SBB M |

A ¬ A - (HL) - CY |

↕ ↕ ↕ ↕ ↕ |

10 011 110 |

9E | 1 |

2 |

7 |

|

| CMP r |

A - r |

↕ ↕ ↕ ↕ ↕ |

10 111 r |

1 |

1 |

4 |

||

| CPI n |

A - n |

↕ ↕ ↕ ↕ ↕ |

11 111 110 |

2 |

2 |

7 |

||

| CMP M |

A - (HL) |

↕ ↕ ↕ ↕ ↕ |

10 111 110 |

BE | 1 |

2 |

7 |

|

ANA r |

A ¬ A and r |

↕ ↕ • ↕ 0 |

10 100 r |

1 |

1 |

4 |

||

ANI n |

A ¬ A and n |

↕ ↕ • ↕ 0 |

11 100 110 |

2 |

2 |

7 |

||

ANA M |

A ¬ A and (HL) |

↕ ↕ • ↕ 0 |

10 100 110 |

A6 | 1 |

2 |

7 |

|

ORA r |

A ¬ A or r |

↕ ↕ • ↕ 0 |

10 110 r |

1 |

1 |

4 |

||

ORI n |

A ¬ A or n |

↕ ↕ • ↕ 0 |

11 110 110 |

2 |

2 |

7 |

||

ORA M |

A ¬ A or (HL) |

↕ ↕ • ↕ 0 |

10 110 110 |

B6 | 1 |

2 |

7 |

|

XRA r |

A ¬ A xor r |

↕ ↕ • ↕ 0 |

10 101 r |

1 |

1 |

4 |

||

XRI n |

A ¬ A xor n |

↕ ↕ • ↕ 0 |

11 101 110 |

2 |

2 |

7 |

||

XRA M |

A ¬ A xor (HL) |

↕ ↕ • ↕ 0 |

10 101 110 |

A6 | 1 |

2 |

7 |

|

| INR r |

r ¬ r + 1 |

↕ ↕ ↕ ↕ • |

00 r 100 |

1 |

1 |

4 |

||

| INR M |

(HL) ¬ (HL) + 1 |

↕ ↕ ↕ ↕ • |

00 110 100 |

34 | 1 |

3 |

11 |

|

| DCR r |

r ¬ r - 1 |

↕ ↕ ↕ ↕ • |

00 r 101 |

1 |

1 |

4 |

||

| DCR M |

(HL) ¬ (HL) - 1 |

↕ ↕ ↕ ↕ • |

00 110 101 |

35 | 1 |

3 |

11 |

|

| DAA | Converts Accumulator contents into packed BCD, following add with packed BCD operands |

↕ ↕ ↕ ↕ ↕ | 00 100 111 |

27 |

1 |

1 |

4 |

|

| CMA |

_ |

• • • • • |

00 101 111 |

2F |

1 |

1 |

4 |

One’s complement. |

| Notes: |

r means any of the registers A, B, C, D, E, H, L. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| DAD B |

HL ¬ HL + BC |

• • • • ↕1 |

00 001 001 |

09 | 1 |

3 |

11 |

|

| DAD D |

HL ¬ HL + DE |

• • • • ↕1 | 00 011 001 |

19 | 1 |

3 |

11 | |

| DAD H |

HL ¬ HL + HL |

• • • • ↕1 | 00 101 001 |

29 | 1 |

3 |

11 | |

| DAD SP |

HL ¬ HL + SP |

• • • • ↕1 |

00 111 001 |

39 | 1 |

3 |

11 | |

| INX B |

BC ¬ BC + 1 |

• • • • • |

00 000 011 |

03 | 1 |

1 |

6 |

|

| INX D |

DE ¬ DE + 1 |

• • • • • |

00 010 011 |

13 | 1 |

1 |

6 |

|

| INX H |

HL ¬ HL + 1 |

• • • • • |

00 100 011 |

23 | 1 |

1 |

6 |

|

| INX SP |

SP ¬ SP + 1 |

• • • • • |

00 110 011 |

33 | 1 |

1 |

6 |

|

| DCX B |

BC ¬ BC - 1 |

• • • • • |

00 001 011 |

0B | 1 |

1 |

6 |

|

| DCX D |

DE ¬ DE - 1 |

• • • • • |

00 011 011 |

1B | 1 |

1 |

6 |

|

| DCX H |

HL ¬ HL - 1 |

• • • • • |

00 101 011 |

2B | 1 |

1 |

6 |

|

| DCX SP |

SP ¬ SP - 1 |

• • • • • |

00 111 011 |

3B | 1 |

1 |

6 |

|

| Notes: |

1 Indicates the flag is affected

by the 16 bit result of the operation. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

|

|

___ |

• • • • ↕ |

00 111 111 |

3F |

1 |

1 |

4 |

Complement |

| STC |

CY ¬ 1 |

• • • • 1 |

00 110 111 |

37 |

1 |

1 |

4 |

|

| NOP |

No Operation |

• • • • • |

00 000 000 |

00 |

1 |

1 |

4 |

|

| HLT |

CPU halted |

• • • • • |

01 110 110 |

76 |

1 |

1 |

4 |

|

| DI1 |

IFF ¬ 0 |

• • • • • |

11 110 011 |

F3 |

1 |

1 |

4 |

|

| EI1 |

IFF ¬ 1 |

• • • • • |

11 111 011 |

FB |

1 |

1 |

4 |

|

| Notes: |

1 No interrupts are issued directly after a DI or EI. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is set |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| JMP nn |

PC ¬ nn |

• • • • • |

11 000 011 |

C3 |

3 |

3 |

10 |

|

| JNZ nn |

if NZ is true, |

• • • • • |

11 000 010 |

3 |

3 |

10 |

||

JZ nn |

if Z is true, |

• • • • • |

11 001 010 |

3 |

3 |

10 |

||

JNC nn |

if NC is true, |

• • • • • |

11 010 010 |

3 |

3 |

10 |

||

JC nn |

if C is true, |

• • • • • |

11 011 010 |

3 |

3 |

10 |

||

JPO nn |

if PO is true, |

• • • • • |

11 100 010 |

3 |

3 |

10 |

||

JPE nn |

if PE is true, |

• • • • • |

11 101 010 |

3 |

3 |

10 |

||

JP nn |

if P is true, |

• • • • • |

11 110 010 |

3 |

3 |

10 |

||

JM nn |

if M is true, |

• • • • • |

11 111 010 |

3 |

3 |

10 |

||

| PCHL |

PC ¬ HL |

• • • • • |

11 101 001 |

E9 |

1 |

1 |

4 |

|

| Flag Notation: |

• = flag is not affected. |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| CALL nn |

SP ¬ SP - 1 |

• • • • • |

11 001 101 |

CD |

3 |

5 |

17 |

|

| CNZ nn |

if NZ is true, |

• • • • • |

11 000 100 |

C4 | 3 |

3 |

10 |

if NZ is false |

CZ nn |

if Z is true, |

• • • • • |

11 001 100 |

CC | 3 |

3 |

10 |

if Z is false if Z is true |

CNC nn |

if NC is true, |

• • • • • |

11 010 100 |

D4 | 3 |

3 |

10 |

if NC is false if NC is true |

CC nn |

if Z is true, |

• • • • • |

11 011 100 |

D8 | 3 |

3 |

10 |

if C is false if C is true |

CPO nn |

if PO is true, |

• • • • • |

11 100 100 |

E4 | 3 |

3 |

10 |

if PO is false if PO is true |

CPE nn |

if PE is true, |

• • • • • |

11 101 100 |

EC | 3 |

3 |

10 |

if PE is false if PE is true |

CP nn |

if P is true, |

• • • • • |

11 110 100 |

F4 | 3 |

3 |

10 |

if P is false if P is true |

CM nn |

if M is true, |

• • • • • |

11 111 100 |

FC | 3 |

3 |

10 |

if M is false if M is true |

| RET |

PCL ¬

(SP) |

• • • • • |

11 001 001 |

C9 |

1 |

3 |

10 |

|

| RNZ |

if NZ is true, |

• • • • • |

11 000 000 |

C0 | 1 |

1 |

5 |

if NZ is false |

| RZ |

if Z is true, |

• • • • • |

11 001 000 |

C8 | 1 |

1 |

5 |

if Z is false |

| RNC |

if NC is true, |

• • • • • |

11 010 000 |

D0 | 1 |

1 |

5 |

if NC is false |

| RC |

if C is true, |

• • • • • |

11 011 000 |

D8 | 1 |

1 |

5 |

if C is false |

| RPO |

if PO is true, |

• • • • • |

11 100 000 |

E0 | 1 |

1 |

5 |

if PO is false |

| RPE |

if PE is true, |

• • • • • |

11 101 000 |

E8 | 1 |

1 |

5 |

if PE is false |

| RP |

if P is true, |

• • • • • |

11 110 000 |

F0 | 1 |

1 |

5 |

if P is false |

| RM |

if M is true, |

• • • • • |

11 111 000 |

F8 | 1 |

1 |

5 |

if M is false |

| RST i |

SP ¬ SP - 1 |

• • • • • |

11 t 111 |

1 |

3 |

11 |

_i_ _t_ __p__ |

|

| Flag Notation: |

• = flag is not affected. |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| RLC |

|

• • • • ↕ |

00 000 111 |

07 |

1 |

1 |

4 |

|

| RAL |

|

• • • • ↕ |

00 010 111 |

17 |

1 |

1 |

4 |

|

| RRC |

|

• • • • ↕ |

00 001 111 |

0F |

1 |

1 |

4 |

|

| RAR |

|

• • • • ↕ |

00 011 111 |

1F |

1 |

1 |

4 |

|

| Notes: |

CY means the carry flip-flop. |

|||||||

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, |

|||||||

| Mnemonic |

Symbolic |

Flags |

Opcode |

Hex |

Bytes |

M |

Clock |

Comments |

| IN n |

A ¬ (n) |

• • • • • |

11 011 011 |

DB |

2 |

3 |

11 |

|

| OUT n |

(n) ¬ A |

• • • • • |

11 010 011 |

D3 |

2 |

3 |

11 |

|

| Flag Notation: |

• = flag is not affected, 0 = flag is reset, 1 = flag is

set, |

|||||||