|

|

||||||||||

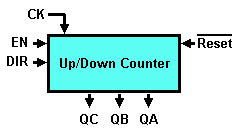

| Progettare un contatore sincrono avanti/indietro modulo 5, utilizzando il simulatore di macchine a stati finiti (Finite State Machine Simulator, d-FsM). Il contatore deve generare ciclicamente, sulle uscite QC, QB e QA, la sequenza da '000' a '100', quando conta in avanti, oppure da '100' a '000', quando conta indietro.

Come si vede nella figura qui sopra:

Potete scaricare qui una traccia del diagramma ASM, dove le variabili di stato X,Y e Z sono già state definite, così come le uscite QC, QB, QA, e gli ingressi DIR e EN. Nella traccia, sono stati definiti anche i cinque blocchi di stato necessari al progetto. Al Reset, il contatore deve partire da '000'. Per questa ragione lo stato 'a' è stato impostato come 'Stato di Reset' (cioè lo stato di partenza, all'attivazione del !Reset asyncrono). E' conveniente, in questo particolare caso, mantenere l'assegnazione degli stati che trovate definita nella traccia (dove X = QC, Y = QB e Z = QA). Verificate, utilizzando la simulazione temporale Terminato il progetto della MSF, potete importare il componente ottenuto nel d-DcS. A questo proposito è qui disponibile la traccia dello schema d-DcS. Infine, vi si chiede di ripetere la simulazione del contatore nel d-DcS timing simulator | |||||||||||

del d-FsM, che le sequenze degli stati e dei valori in uscita siano corrette.

del d-FsM, che le sequenze degli stati e dei valori in uscita siano corrette.  .

.