Combinational Network Design

2.2 Using Maps for AND-OR Synthesis

2.2.3 “Checkerboard” Maps

Network corresponding to the map synthesis:

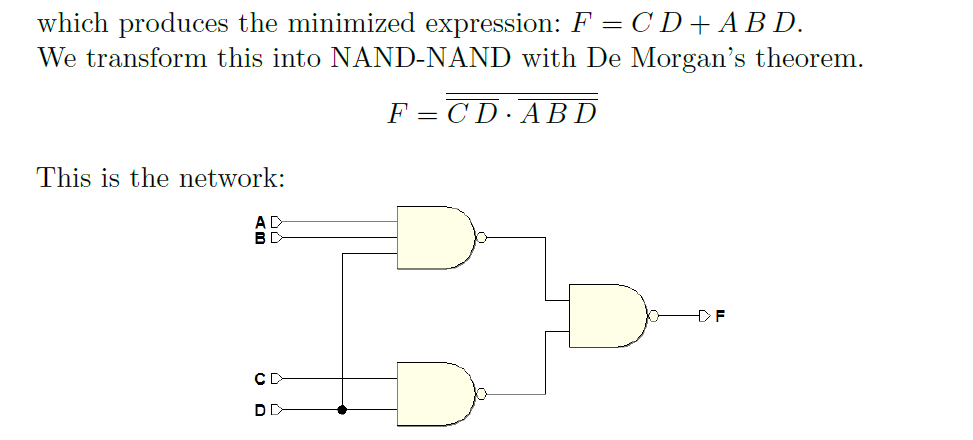

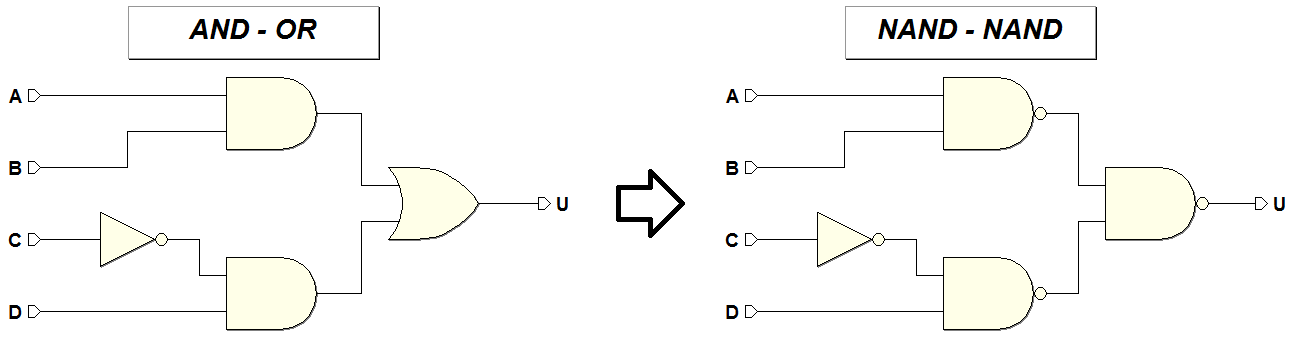

2.4 NAND-NAND Synthesis

Proof and Equivalence

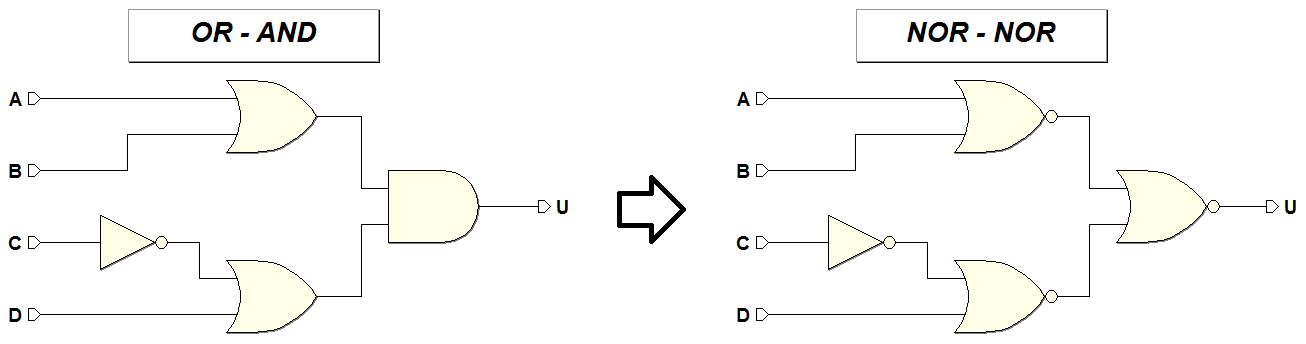

2.5 NOR-NOR Synthesis

Equivalence

2.6 Standard Combinational Networks

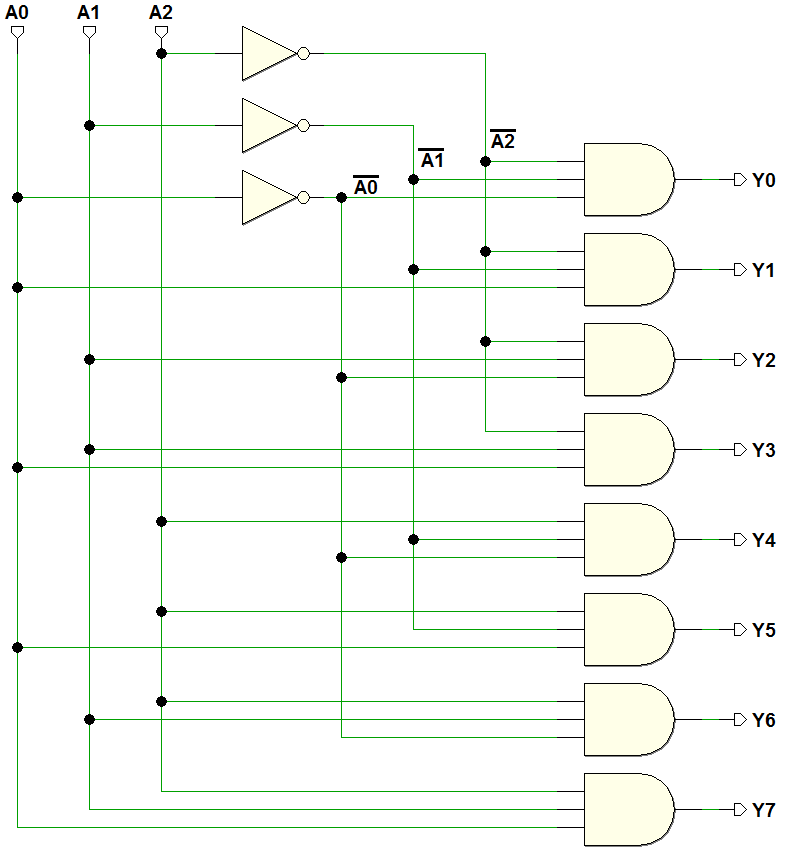

2.6.1 Decoders

Synthesis of the decoder 3-8

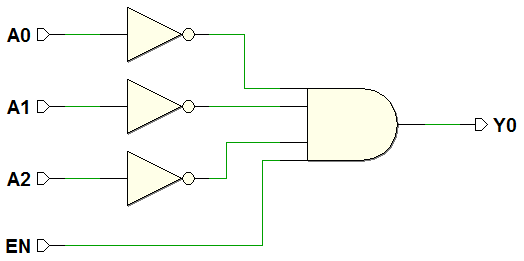

Synthesis of the output Y0 of the decoder 3-8

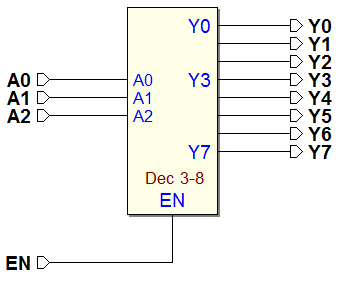

A component: decoder 3-8 with Enable

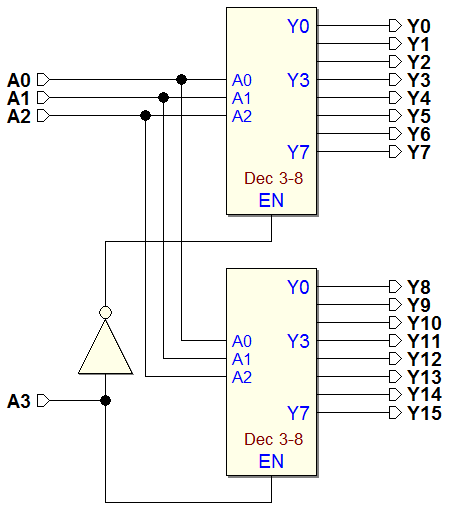

A decoder 4-16, using two decoders 3-8

2.6.2 Multiplexers

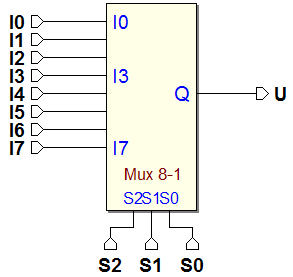

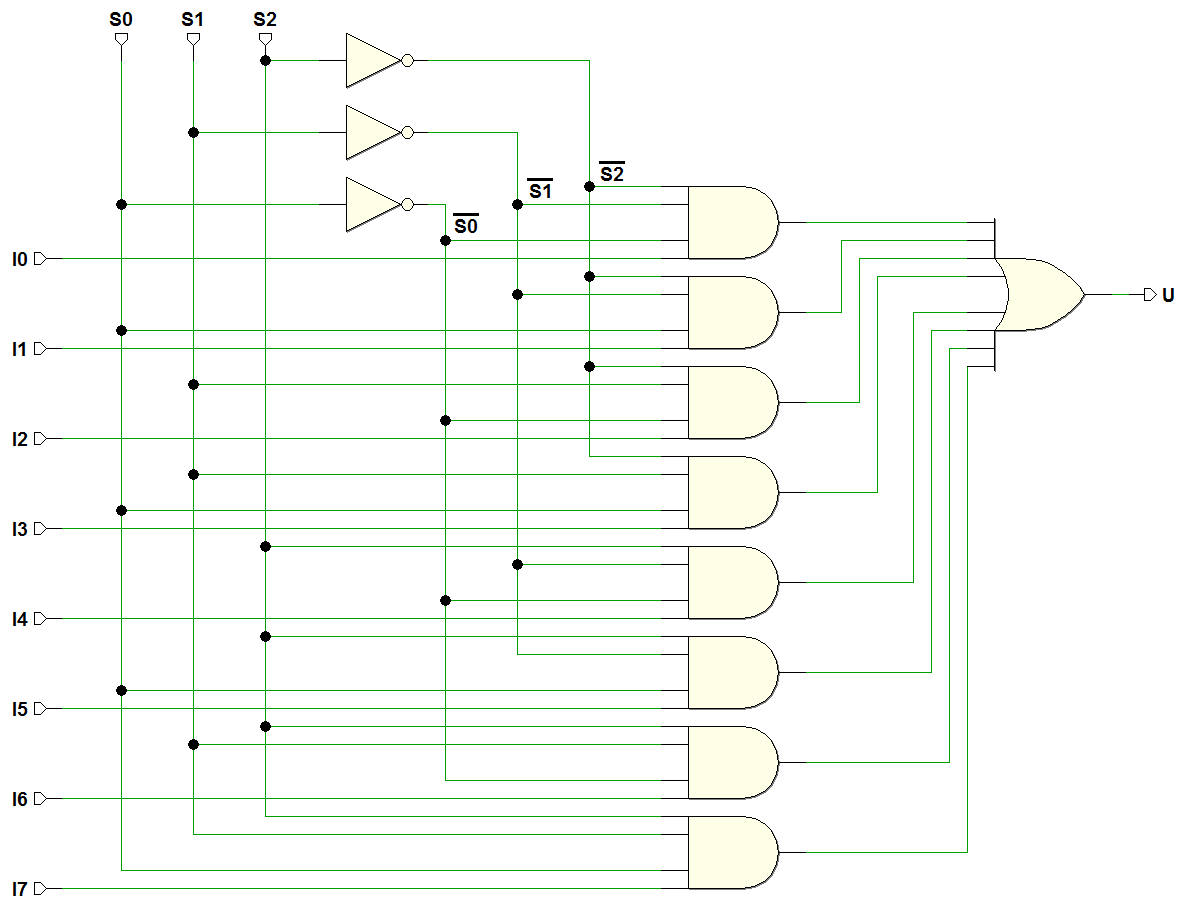

Multiplexer 8-1

Multiplexer 8-1: synthesis using a decoder

Multiplexer 8-1: two-level synthesis

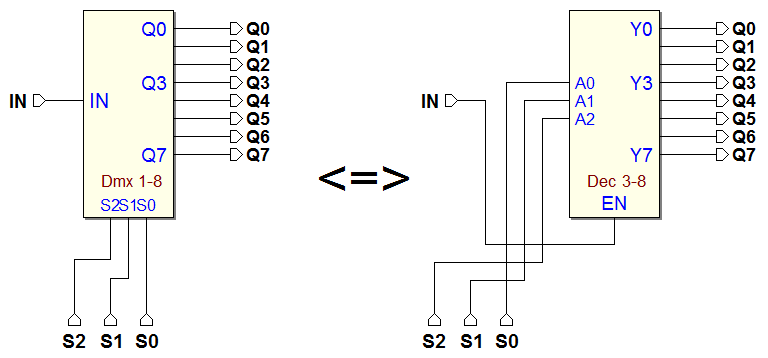

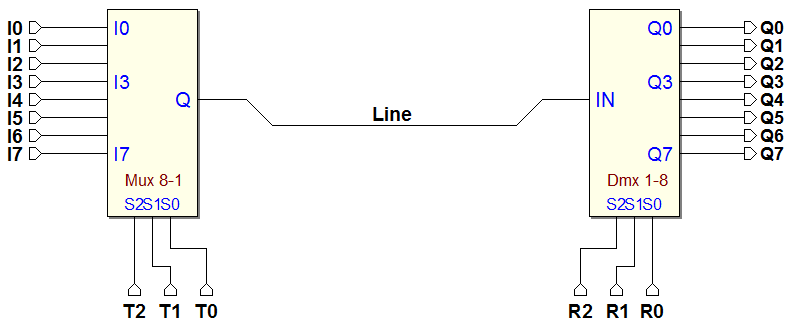

2.6.3 Demultiplexers

Demultiplexers 1-8

Equivalence demultiplexer - decoder

Example

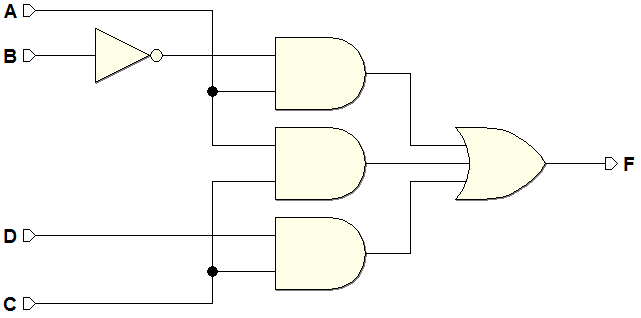

2.6.6 Using Multiplexers to Synthesize Combinational Networks

Example 1

Example 2

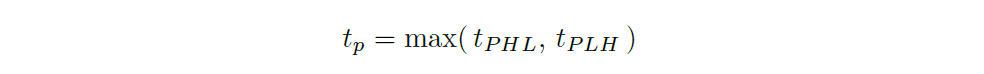

2.8 Time Behavior of Combinational Networks

2.8.1 Definitions and Timing Models

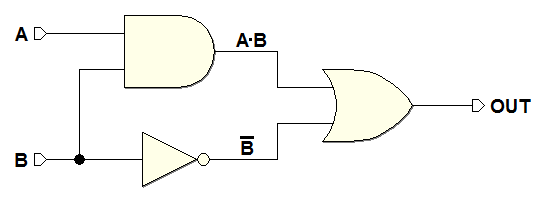

Basic example

Transport delays evaluation

2.8.2 Hazards

Not, AND

Not, OR

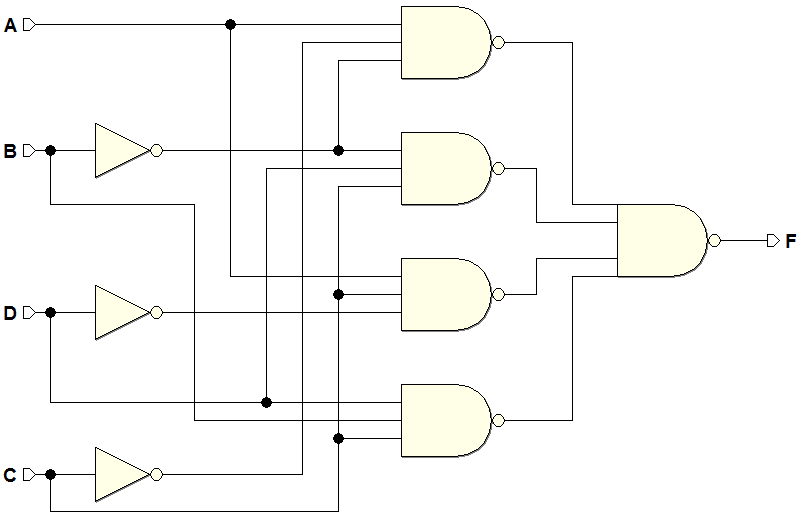

2.8.3 Elimination of Static Hazards

With hazard

Without hazard

2.9 Exercises

2.9.2 Hazards

Exercise 2

2.10 Solutions

2.10.1 Maps

Exercise 8

2.10.2 Hazards

Exercise 2

2. Errata Corrige (Chapter 2)

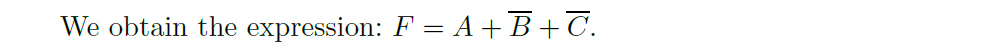

Page 64

On the center of the page, the correct expression is:

Page 75

Solution of exercise 5. Read as follows:

Page 76

After the map, read as follows: