|

|

|||||||||

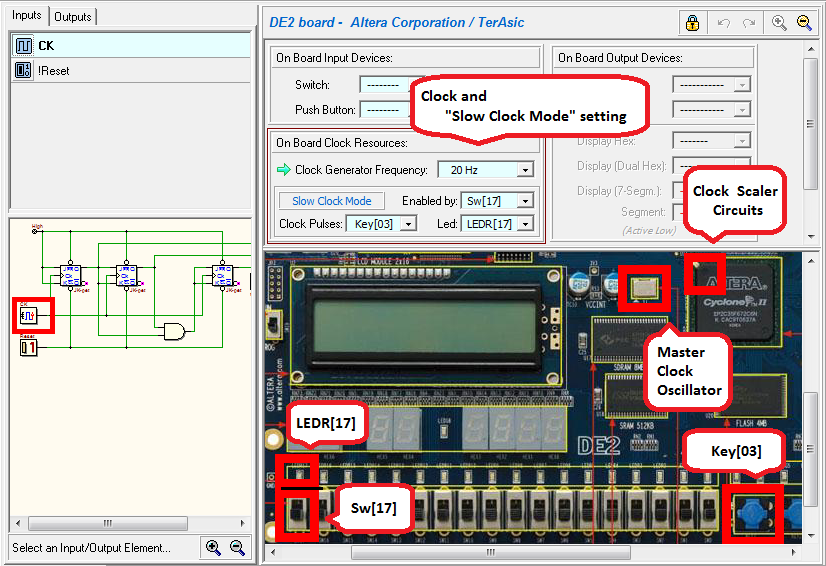

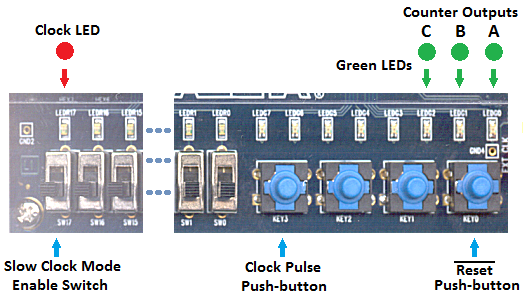

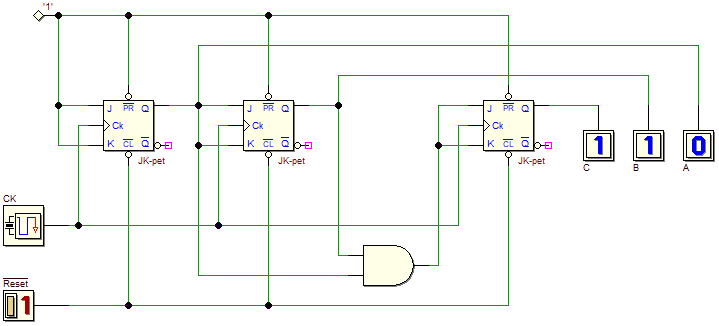

| Prima di proseguire, si consiglia di avere letto la pagina: In questa pagina consideriamo le possibilità offerte dal DEEDS per il test di reti sequenziali implementate su di una scheda FPGA di tipo Terasic/Altera DE2. Scegliamo, come esempio di lavoro, una rete sequenziale semplice, per concentrare l'attenzione sulla metodica di test: un contatore binario a 3 bit. Ipotizziamo di averne progettato la rete, come risulta nello schema seguente (un click sulla figura aprirà lo schema nel Deeds-DcS): E' utile verificare la funzionalità della rete nel Deeds-DcS, utilizzando sia la simulazione per animazione Implementiamo ora il contatore sulla scheda DE2. Nel Deeds-DcS, tramite il comando "Test on FPGA", apriamo la finestra di dialogo visibile qui sotto. Nel nostro esempio, tutte le associazioni degli ingressi e uscite con i corrispondenti dispositivi della scheda sono state già predefinite. In questa figura è evidenziata l'associazione del clock della rete con i dispositivi sulla scheda DE2. La frequenza del clock è stata scelta molto bassa (20 Hz), in modo da permettere un esame visivo del funzionamento del contatore (le sue uscite sono state assegnate a 3 LED verdi, vedi la figura riassuntiva più sotto). E' stata predisposta anche la modalità di esecuzione a clock rallentato ("Slow Clock Mode"), assegnando l'interruttore Sw[17] al compito di abilitare (al "run time") tale funzione. E' stato predisposto anche un LED, il LEDR[17], come visualizzatore degli impulsi di clock che saranno inviati alla rete; infine, è stato scelto il pulsante Key[03] come comando manuale di generazione degli impulsi di clock (invece di impostare un pulsante, si poteva attivare una cadenza automatica di generazione, da un impulso ogni 10 secondi a 5 impulsi al secondo). Se l'interruttore Sw[17] è posizionato a '0', la funzione di clock rallentato non è attiva e la rete funziona con il clock "normale" (20 Hz). Se l'interruttore Sw[17] è posto a '1', il sistema ferma la generazione del clock e resta in attesa che l'utente prema il pulsante Key[03]. Ad ogni pressione del pulsante viene generato un impulso di clock (un fronte di salita alla pressione, seguito da un fronte di discesa). Se si tiene premuto a lungo il pulsante, l'operazione di generazione dell'impulso è ripetuta automaticamente, con la frequenza di circa due impulsi al secondo. Il LED selezionato si accende in corrispondenza del livello alto del clock, per rendere visibile all'utente la generazione degli impulsi. Per ottimizzare la sperimentazione di quanto descritto sulla scheda FPGA, le associazioni sono evidenziate in modo riassuntivo nella figura seguente (il "pannello di controllo" del nostro sistema): Per approfondire il tema del test di microcomputer su FPGA, si consiglia di leggere anche la seguente pagina:

|

||||||||||

, che quella temporale

, che quella temporale  . Una appropriata sequenza di test è disponibile nella finestra del diagramma temporale. Si raccomanda di usare lo schema fornito senza cancellare o modificare le terminazioni di ingresso e di uscita perché sono state predisposte per la esportazione del progetto sulla scheda FPGA.

. Una appropriata sequenza di test è disponibile nella finestra del diagramma temporale. Si raccomanda di usare lo schema fornito senza cancellare o modificare le terminazioni di ingresso e di uscita perché sono state predisposte per la esportazione del progetto sulla scheda FPGA.