|

|

|||||||||||||||||

|

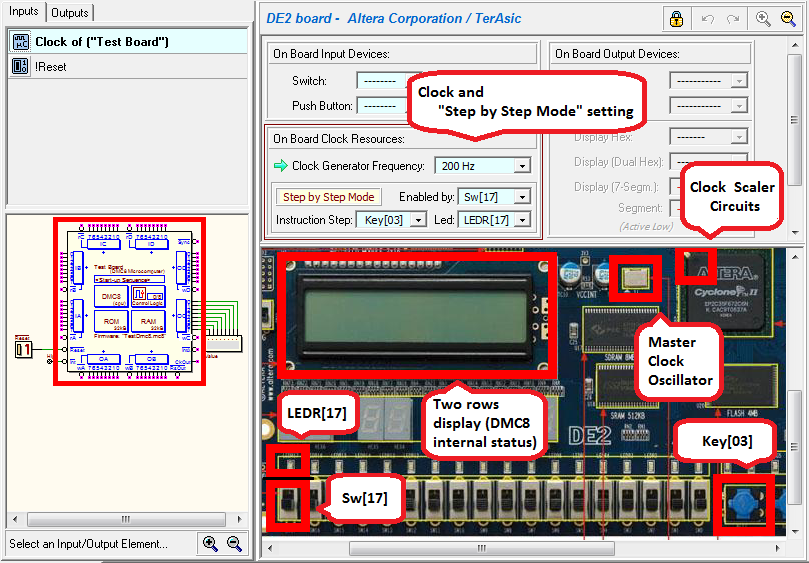

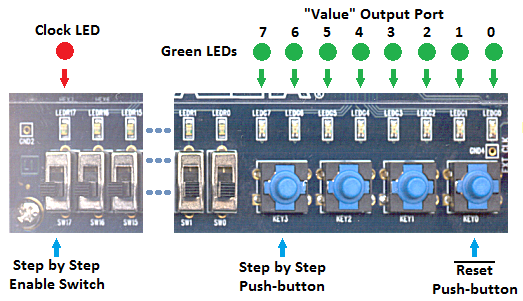

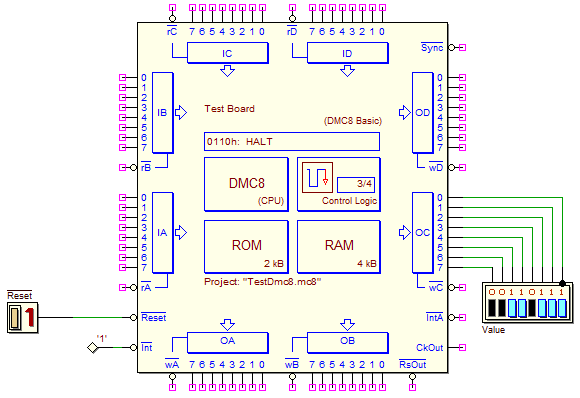

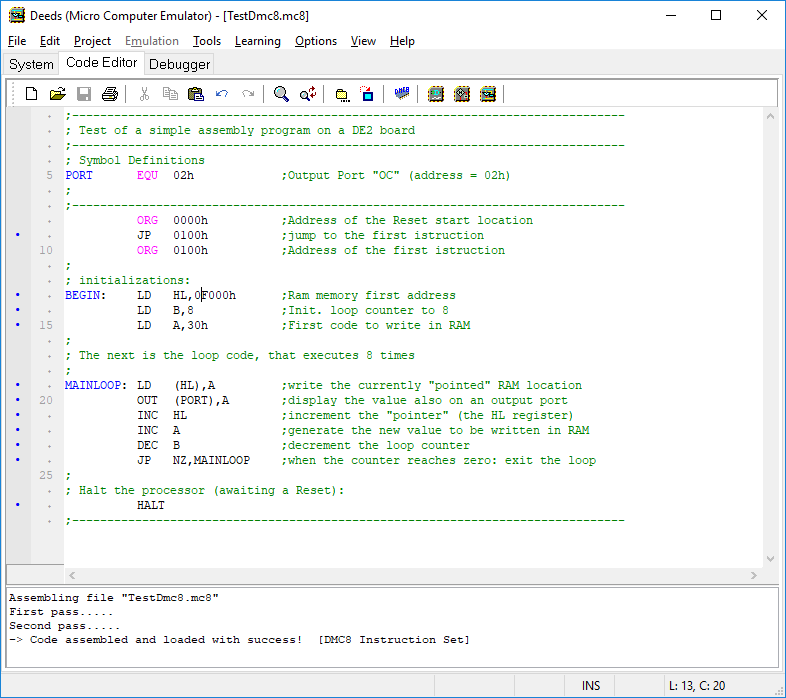

Prima di proseguire, si consiglia di avere letto le pagine: In questa pagina vengono esaminate le possibilità offerte dal DEEDS per il test di un sistema basato sul microcomputer DMC8 e implementato su di una scheda FPGA di tipo Terasic/Altera DE2 . Per focalizzare l'attenzione sulla metodica di testing, utilizziamo, quale esempio di lavoro, una implementazione semplice, sia dal punto di vista hardware che software. Dobbiamo immaginare che questo circuito sia il risultato di un nostro lavoro di progetto, e che tutte le specifiche definite nel problema di partenza siano state verificate da un punto di vista funzionale, mediante simulazione della rete (interattiva o temporale). Il sistema che consideriamo è il seguente, dove un microcomputer DMC8, in versione base, è collegato ad un visualizzatore a 8 LED tramite un porto parallelo di uscita, oltre che ad un pulsante di Reset (un click sulla figura aprirà lo schema nel Deeds-DcS): Il programma che specializza il funzionamento del microcomputer è riportato qui di seguito (un click sulla figura aprirà il programma nel Deeds-McE): Come spiegato nei commenti del programma stesso, al Reset del sistema sono inizializzati tre registri. Il sistema è stato configurato con 2 KB di ROM e 4 KBytes di RAM. HL è impostato all'indirizzo della prima locazione di RAM disponibile (F000h), B al numero di volte che il ciclo che segue sarà eseguito e, infine, A al primo dei codici che, come vedremo, saranno scritti nella memoria. Il programma prosegue con l'esecuzione del ciclo principale (MAINLOOP) che scrive, in 8 locazioni di memoria contigue (a partire da quella di indirizzo F000h), i codici ASCII delle prime cifre numeriche decimali (da '0' a '7': 30h, 31h, 32h, 33h, 34h, 35h, 36h, 37h), in ordine crescente. Per ragioni di test, ad ogni "giro" del ciclo, il valore viene non solo scritto in memoria, ma anche replicato in uscita, tramite il porto "PORT". Infine, il processore viene fermato con una HALT, in attesa di un successivo reset del sistema. E' utile effettuare la simulazione del sistema nel Deeds-DcS, utilizzando sia la simulazione per animazione Iniziamo la procedura per realizzare fisicamente il sistema sulla scheda DE2. Nel Deeds-DcS, tramite il comando "Test on FPGA", apriamo la finestra di dialogo visibile qui sotto. In questo esempio, tutte le associazioni degli ingressi e uscite con i corrispondenti dispositivi della scheda sono state già predefinite. In questa figura è messa in evidenza l'associazione del microcomputer con i componenti presenti sulla scheda DE2. E' stato scelto un clock a frequenza molto bassa (200 Hz), tale da permettere l'osservazione visiva della configurazione di uscita sul porto (associato a 8 LED verdi, vedi la figura riassuntiva più sotto). E' stata anche predisposta la modalità di esecuzione passo-passo ("Step by Step Mode"), assegnando l'interruttore Sw[17] al compito di abilitare (al "run time") tale funzione. E' stato predisposto anche un LED, il LEDR[17], come visualizzatore degli impulsi di clock che saranno inviati al microcomputer; infine, è stato scelto il pulsante Key[03] come comando manuale dell'avanzamento delle istruzioni. Invece di impostare un pulsante, si poteva anche attivare una cadenza automatica di esecuzione (da una istruzione ogni 10 secondi a 5 istruzioni al secondo). Se l'interruttore Sw[17] è posizionato a '0', la funzione di debug non è attiva e il microcomputer funziona con il clock "normale" (200 Hz, nel nostro esempio). Se l'interruttore Sw[17] è a '1', il clock del processore è inibito, e il sistema di debug resta in attesa che l'utente prema il pulsante Key[03]. Ad ogni pressione del pulsante, il microcomputer esegue una istruzione. Per ottenere questo, il debugger invia al microcomputer tanti fronti di clock quanti ne bastano per eseguirla, fino a fermarsi alla fine della fase di prelievo (fetch) della prossima, senza eseguirla. Se si tiene premuto a lungo il pulsante, l'operazione di avanzamento è ripetuta automaticamente, alla cadenza di circa due istruzioni al secondo. Il LED lampeggia al momento di eseguire una istruzione, per confermare all'utente l'esecuzione della istruzione corrente. Al completamento della esecuzione di una istruzione, il debugger legge lo stato interno del processore e lo riporta sul display alfanumerico della scheda. Dal momento che questo è provvisto solo di 2 righe e 16 colonne, non è possibile visualizzare il contenuto di tutti i registri insieme, per cui questa informazione è rappresentata per pagine, che si alternano ciclicamente. La tabella seguente mostra un esempio di visualizzazione delle pagine:

Per ottimizzare la sperimentazione di quanto descritto sulla scheda FPGA, le associazioni sono evidenziate in modo riassuntivo nella figura seguente (il "pannello di controllo" del nostro sistema): |

||||||||||||||||||

, che quella temporale

, che quella temporale  . A questo proposito è disponibile nella finestra del diagramma temporale una appropriata sequenza di test. Si raccomanda di usare lo schema fornito senza cancellare o modificare le terminazioni di ingresso e di uscita perché sono state predisposte per la esportazione del progetto sulla scheda FPGA.

. A questo proposito è disponibile nella finestra del diagramma temporale una appropriata sequenza di test. Si raccomanda di usare lo schema fornito senza cancellare o modificare le terminazioni di ingresso e di uscita perché sono state predisposte per la esportazione del progetto sulla scheda FPGA.