|

|

|||||||||

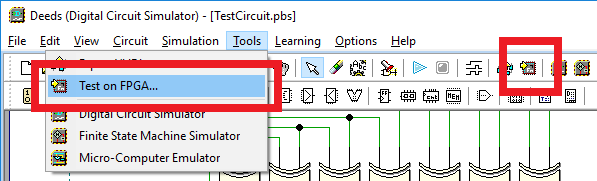

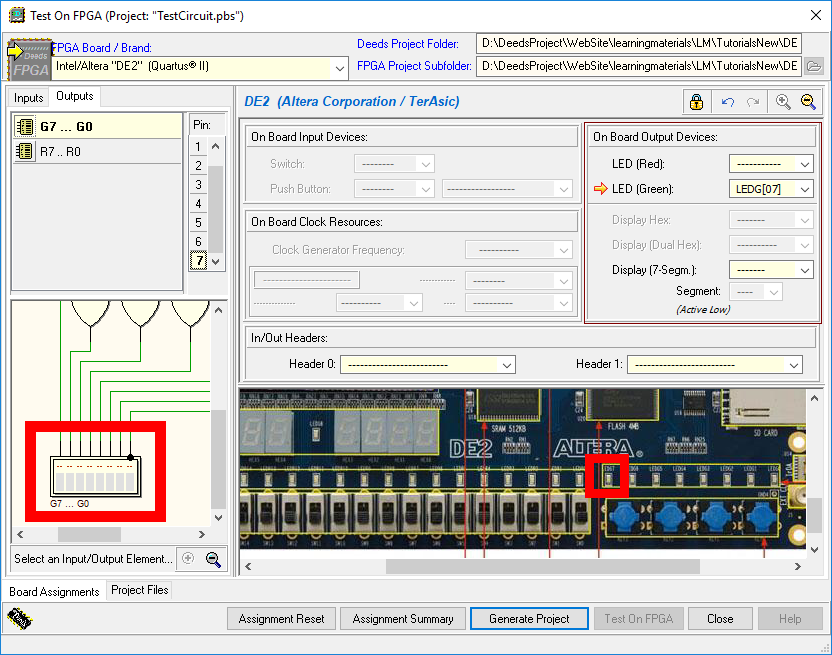

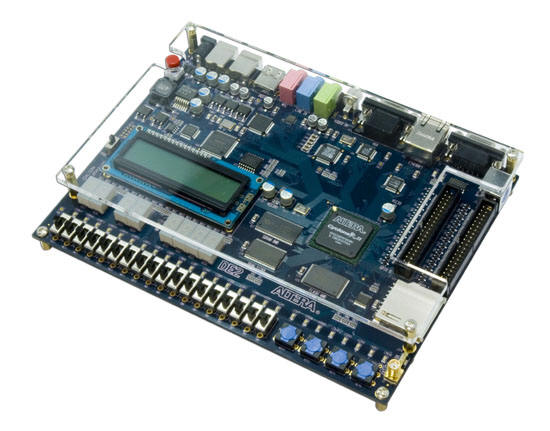

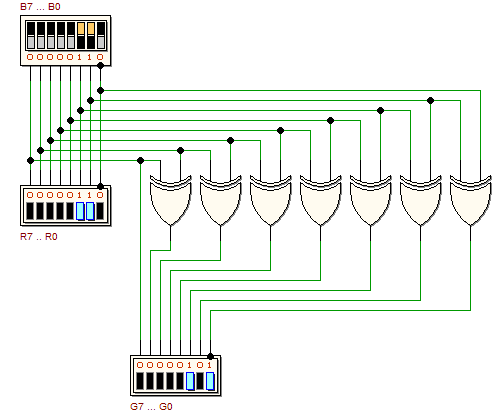

| In questa pagina esamineremo i passi necessari per implementare un progetto DEEDS su di una scheda FPGA di tipo Terasic/Altera DE2, al fine di realizzare fisicamente un prototipo del progetto e verificarne il reale funzionamento. La scheda Terasic/Altera DE2 è pensata per la sperimentazione di circuiti digitali, anche molto complessi, e comprende numerosi dispositivi, dai più semplici (interruttori, pulsanti, LED, display a sette segmenti) ai più elaborati (display a matrice LCD, interfaccia di rete Ethernet, interfacie USB 2.0 di tipo A e B, interfaccia SD, ingressi e uscite audio analogiche, ingresso video analogico, uscita video VGA, e altro). Il cuore della scheda è rappresentato da un dispositivo programmabile FPGA ("Field Programmable Gate Array"), di tipo Intel/Altera Cyclone® II 2C35, contenente più di 30.000 unità logiche (LE, Logic Elements). La scheda DE2 permette di realizzare da semplici progetti introduttivi (in cui usa una piccola parte delle sue potenzialità), a sistemi complessi che possono includere microcomputer e interfacce specializzate. Per concentrare l'attenzione sulla metodica di implementazione del prototipo, utilizziamo, quale esempio di lavoro, un circuito molto semplice. Dobbiamo immaginare che questo circuito sia il risultato di un nostro lavoro di progetto, e che tutte le specifiche definite nel problema di partenza siano state verificate da un punto di vista funzionale, mediante simulazione della rete (interattiva o temporale). Il circuito che prendiamo come esempio è un semplice convertitore di codice a 8 bit, da binario naturale a codice Gray (un click sulla figura seguente aprirà lo schema nel Deeds-DcS): L'ingresso è rappresentato dagli 8 bit B7, B6, B5, B4, B3, B2, B1 e B0. E' utile effettuare la simulazione del sistema nel Deeds-DcS, utilizzando sia la simulazione per animazione A questo punto inizia la procedura per realizzare fisicamente il progetto sulla scheda DE2. Nel Deeds-DcS è disponibile il comando "Test on FPGA" (evidenziato nella figura seguente, sia nel menù "Tools", che nella barra dei comandi): Il comando "Test on FPGA" apre la finestra di dialogo visibile qui sotto:

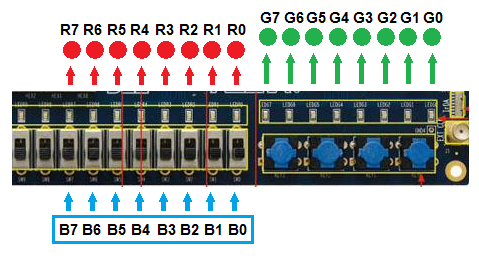

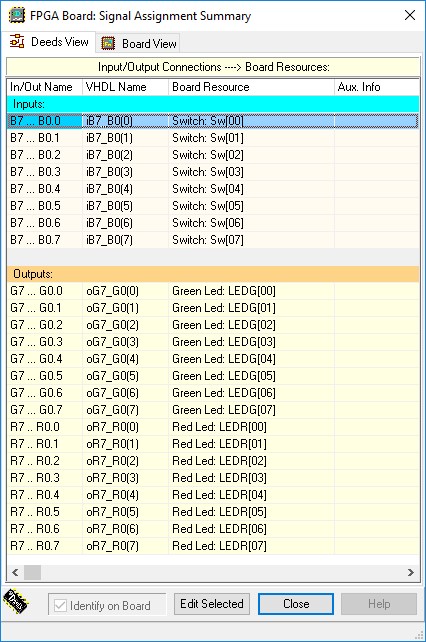

In questa finestra si sceglie prima di tutto la scheda FPGA che si intende usare (in alto a sinistra); è poi possibile associare ad ogni ingresso e uscita dello schema Deeds-DcS (visibile sulla sinistra) una delle risorse disponibili sulla scheda (sulla destra della finestra). L'evidenziazione grafica dei vari oggetti coinvolti aiuta in questo processo di assegnazione. Per riferimento e per approfondire la conoscenza della scheda DE2, è possibile scaricare, in formato PDF, il manuale della scheda (in inglese). Tutte le necessarie associazioni tra lo schema Deeds-DcS e la scheda FPGA sono già state definite, per cui non è necessario modificarle. Per migliorare la sperimentazione sulla scheda, le associazioni sono evidenziate anche nella figura seguente, che possiamo considerare come una sorta di "pannello di controllo" del nostro dispositivo. Questa figura sarà utile, come riferimento visivo, nel momento in cui passeremo al test sulla scheda: Otto degli interruttori disponibili, Sw[07]..Sw[00] (nomenclatura del costruttore), sono stati associati agli ingressi B7.. B0; gli otto LED rossi LEDR[07]..LEDR[00] sono stati assegnati alle uscite R7..R0, e infine gli otto LED verdi LEDV[07]..LEDV[00] alle uscite G7..G0. Premendo con il mouse il pulsante "Assignment summary", possiamo esaminare, in forma di tabella, tutte le associazioni effettuate, sia dal punto di vista dello schema, via dal punto di vista della scheda:

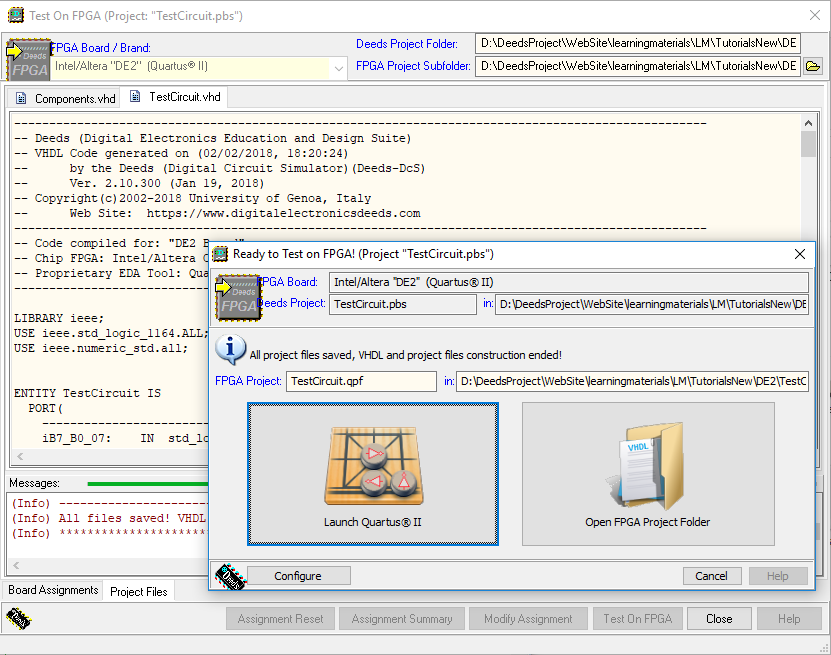

Premendo ora il pulsante "Generate Project", il Deeds-DcS genererà tutto il codice VHDL e i file di progetto necessari per il software Quartus® II, della Intel/FPGA (già Altera Corporation). Il VHDL è uno dei linguaggi utilizzati per la descrizione dell'hardware (HDL: Hardware Description Language), ed è usato correntemente per il progetto di sistemi digitali complessi.

Quartus® II è disponibile in versione gratuita in edizione web (ver. 13.0 sp1) e deve essere stato installato sul computer su cui state lavorando. E' un software molto potente, con molte possibilità, e che contiene numerosi tools di sviluppo predisposti per la progettazione di un sistema digitale realizzato con FPGA. Nei nostri esperimenti ci limiteremo ad usarne le funzionalità essenziali per trasferire il nostro progetto sul chip FPGA della scheda DE2. Terminata la generazione dei file VHDL, questi compaiono nella finestra, suddivisi in pagine differenti, come visibile qui sotto. Una finestra di dialogo (quella in primo piano) ci chiede di lanciare il software Quartus® II.

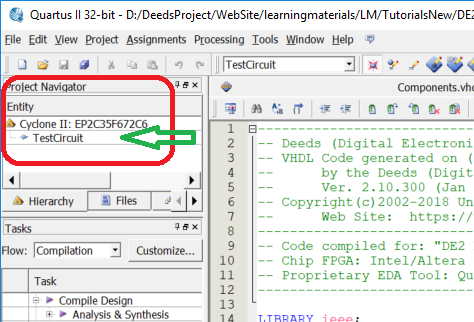

Dopo avere lanciato Quartus® II, nella sua finestra principale, in alto a sinistra, si legge la sigla del componente FPGA Cyclone® II utilizzato sulla scheda DE2 e la entità "top level" del progetto:

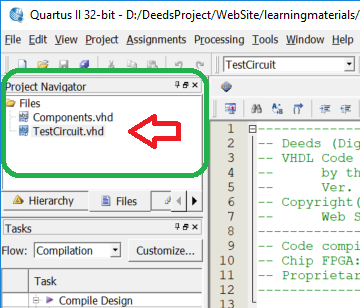

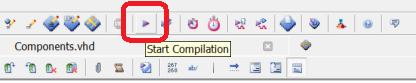

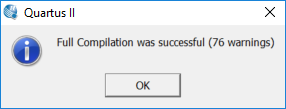

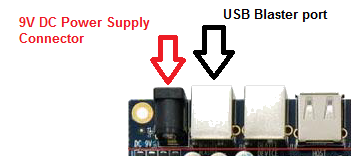

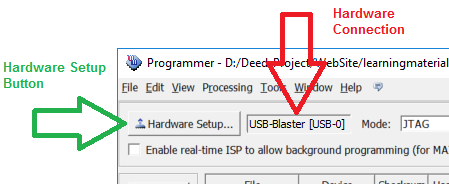

In Quartus® II è ora aperto il project "TestCircuit.qpf", uno dei file che il Deeds ha generato (.qpf = "Quartus Project File"); questo file definisce l'entità "top level" del progetto. Il Deeds ha generato anche il file "TestCircuit.qsf", che Quartus® II utilizza per tutte le informazioni rilevanti ai fini della sintesi del progetto, come ad esempio l'elenco dei file VHDL da compilare, e le assegnazioni dei collegamenti degli ingressi e delle uscite ai dispositivi fisici della scheda (interruttori, pulsanti, led, ecc.). Un click sul tab "Files" ci mostra i file VHDL associati al progetto (in casi più complessi, i file potrebbero essere molti di più). Un doppio click sui loro nomi permette di esaminarne i contenuti nell'editor. Nel nostro esempio, il file "TestCitcuit.vhd" è una descrizione in VHDL strutturale della rete digitale, e corrisponde allo schema della rete. Il pulsante di "Start Compilation", nella barra dei comandi di Quartus® II, fa partire la compilazione del progetto: Durante la compilazione, nella finestra principale di Quartus II il riquadro "Tasks" ci informa sul progresso della compilazione. Il riquadro in basso, invece, riporta i messaggi del compilatore. A fine compilazione saremo avvisati con una finestra come questa (in questo esempio, ignoreremo i messaggi di avviso): A questo punto è necessario trasferire il risultato della compilazione alla scheda DE2, per far sì che il chip FPGA sia configurato per realizzare fisicamente il nostro progetto. La scheda deve essere alimentata, collegando il suo alimentatore ad una presa elettrica ed all'ingresso "DC 9V" della scheda. Il trasferimento dei dati avviene attraverso il cavo USB collegato al personal computer e all'ingresso "USB Blaster" della scheda: Infine, si può mettere in funzione la DE2 tramite il suo pulsante rosso a sinistra in alto. Non appena alimentata, la DE2 esegue un programma di test che accende alternativamente i led, presenta sui display a sette segmenti i numeri da zero a nove e il messaggio "Welcome to the DE2 board" sulla matrice LCD. Un click sulla icona "Programmer" inizia le operazioni per la configurazione del chip FPGA: Si apre una finestra per stabilire la comunicazione con l'hardware. Nella figura che segue è messa in evidenza la parte della finestra di nostro interesse:

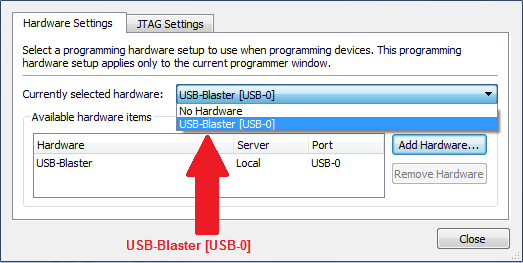

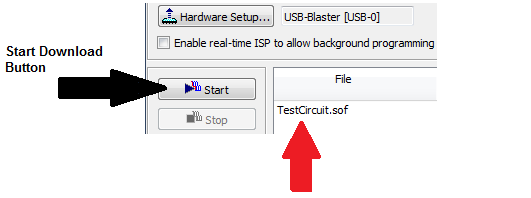

Il tipo di connessione deve essere impostata su "USB-Blaster" (freccia rossa nella figura). Nel caso risultasse "No hardware", o altro, occorre accendere la scheda DE2, se non fosse già accesa, e fare click sul pulsante "Hardware Setup". Apparirà la seguente finestra: Come suggerito dalla figura, occorre indicare come "hardware correntemente selezionato" la "USB-Blaster [USB-0]". Torniamo ora alla finestra del programmatore: Facciamo click sul pulsante "Start", come indicato dalla freccia nera: il file "TestCircuit.sof", che è stato generato in precedenza, dalla compilazione del nostro progetto, verrà trasferito nella scheda DE2, rimpiazzando la configurazione di test di default. Osserverete che sulla scheda il led blu "Load" si accenderà per un breve tempo. A questo punto, la DE2 è "diventata" il nostro circuito! Per approfondire il tema del test dei progetti Deeds su FPGA, si consiglia di leggere anche le seguenti pagine: |

||||||||||

, che quella temporale

, che quella temporale  . A questo proposito è disponibile nella finestra del diagramma temporale una sequenza di test di 16 numeri (da 0 a 15dec). Si raccomanda di usare lo schema fornito senza cancellare o modificare le terminazioni di ingresso e di uscita perchè, come vedremo nel seguito, sono state predisposte per la esportazione del progetto sulla scheda.

. A questo proposito è disponibile nella finestra del diagramma temporale una sequenza di test di 16 numeri (da 0 a 15dec). Si raccomanda di usare lo schema fornito senza cancellare o modificare le terminazioni di ingresso e di uscita perchè, come vedremo nel seguito, sono state predisposte per la esportazione del progetto sulla scheda.