|

|

||||||||||

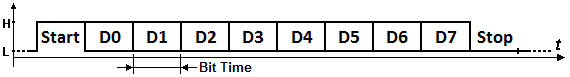

In questo laboratorio si chiede di scrivere un programma, in assembly DMC8, che emuli un ricevitore seriale asincrono. Il ricevitore attende e decodifica pacchetti di bit, come descritto nella figura seguente:

Un pacchetto è composto da:

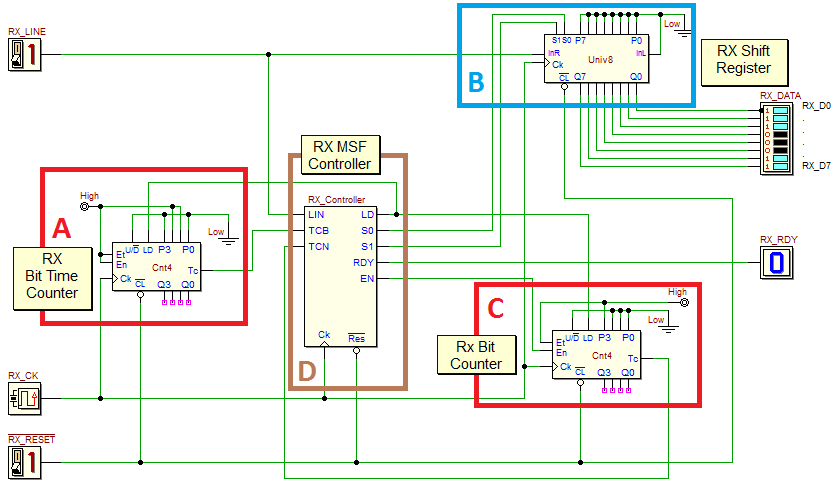

La prossima figura mostra una prima versione del ricevitore, basata su di una macchina a stati finiti (un click sulla figura aprirà lo schema nell'editor del d-DcS): Il sistema è composto da un contatore del tempo di bit [A, evidenziato in rosso], sulla sinistra della figura, un registro a scorrimento [B, in blu, a destra in alto], un contatore nel numero di bit [C, in rosso, sulla destra], e un controllore [D, in marrone, basato su di una macchina a stati finiti].

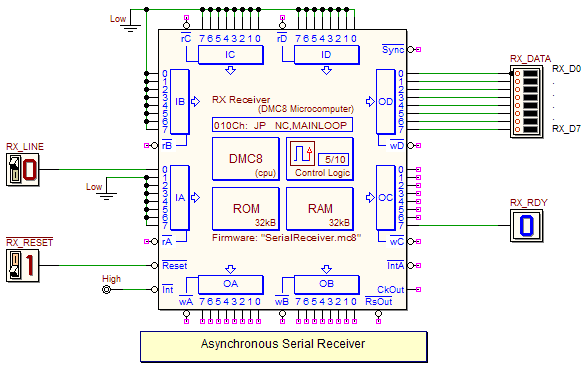

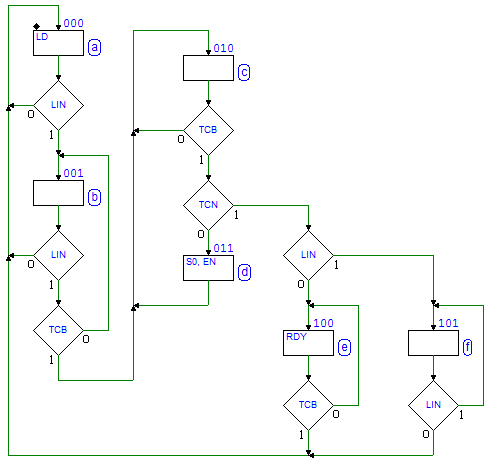

La frequenza di clock del controllore è pari a 16 volte la velocità di bit del pacchetto ricevuto. Per catturare il bit di start, il controllore campiona, nello stato (a), ad ogni ciclo di clock, il suo ingresso LIN (collegato a RX_LINE). Quando LIN passa a uno, il controllore continua a leggerne il valore, nello stato (b). Se LIN, al raggiungimento della metà del tempo di bit, è ancora a uno, il controllore dichiara valido il bit di start, passando nello stato (c). Altrimenti, se nel frattempo LIN ritorna basso, il controllore ricomincia daccapo, mettendosi nuovamente in attesa di un nuovo bit di start. Si noti che la metà del tempo di bit è segnalata dalla linea TCB, che è generata dal contatore del tempo di bit, inizializzato nello stato (a) al valore di partenza '0110' (per mezzo della linea LD). Come risultato di questa inizializzazione, la prima occorrenza di TCB è generata dopo solo la metà del tempo di bit; successivamente, invece, l'attivazione di TCB avviene allo scadere di un tempo di bit completo (cioè ogni 16 cicli di clock, a causa della ciclicità del contatore, a partire dalla metà del bit di start). Lo stato (c) ha il compito di sincronizzare l'acquisizione dei bit dalla linea seriale ed il loro scorrimento nel registro di ricezione. Infatti, quando TCB è attivato, il controllore si sposta nello stato (d): generando S0 = '1' e S1 = '0', ottiene l'acquisizione del dato presente in quel momento su RX_LINE (tramite InR del componente Univ8) e, allo stesso tempo, lo scorrimento a destra di tutti gli altri bit memorizzati nel registro. Dallo stato (c) si esce, poi, quando è attivato TCN, ossia dopo avere acquisito 8 bit. TCN è infatti generato dal contatore dei bit quando raggiunge lo zero, e cioè quando i bit da ricevere sono terminati. Si osservi che tale contatore è decrementato nello stato (d), attivando EN, ogni volta che un bit è acquisito nel registro a scorrimento. Il prossimo compito dell'algoritmo riguarda la verifica del bit di stop. Nello stato (c), quando TCB è attivato, ma è attivo anche TCN (perchè tutti i bit sono stati ricevuti), invece di acquisire il bit di stop nel registro a scorrimento , il controllore ne testa direttamente il suo valore. Se il bit di stop è zero, il formato del pacchetto si assume valido, ed è generato il segnale RX_RDY, passando nello stato (e) e rimandovi per la durata di un tempo di bit. Altriumenti, se il bit di stop è alto, i bit ricevuti vengono ignorati (non generando il segnale RX_RDY) e l'algoritmo riparte dallo stato (a). Infine, lo stato di attesa (f) permette di risolvere in modo semplice lo stato di errore dovuto al bit di stop errato: qui il controllore attende che la linea LIN sia tornata bassa, prima di attendere l'arrivo del prossimo bit di start (sebbene questa non sia la soluzione migliore per gestire la ricezione di un bit di stop errato). Il circuito può essere testato con il simulatore del d-DcS, sia in modalità animazione L'analisi e la simulazione del comportamento del circuito è utile, adesso, per realizzarne una nuova versione, avente le stesse funzionalità, ma basata su di un microcomputer DMC8. Lo schema della nuova versione è visibile nella figura seguente. Un click su di questa aprirà lo schema nel d-DcS. In questo circuito la linea RX_LINE è ricevuta sul bit 0 del porto di ingresso IA del microcomputer. Utilizziamo il porto OD per collegarci alle linee di uscita RX_DATA, e il bit 7 del porto OC, per generare l'uscita RX_RDY. Si noti che nessun altro componente è utilizzato, e che non è collegato al microcomputer nessun clock esterno (vedi RX_CK nello schema originale). Tutti gli intervalli di tempo necessari sono valutati dal microcomputer mediante l'uso delle tecniche delle routine di ritardo (la frequenza di clock del microcomputer è 10 MHz). Un click aprirà una traccia di una possibile realizzazione del programma in assembly. Una volta terminata la scrittura e il test del programma nel d-McE, potrà essere caricato nella ROM del microcomputer, al fine di simulare la nuova versione del trasmettitore nel d-DcS. Anche in questo caso, una sequenza di test ("Rx_Sequence") è predisposta nella finestra del diagramma temporale. | |||||||||||

Contatore del tempo di bit [A]

Contatore del tempo di bit [A]

che temporale

che temporale  . Una opportuna sequenza di test è disponibile nella finestra del diagramma temporale.

. Una opportuna sequenza di test è disponibile nella finestra del diagramma temporale.