|

|

||||||||||

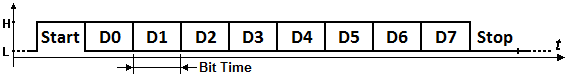

| In questo laboratorio si chiede di scrivere un programma, in assembly DMC8, che emuli un trasmettitore seriale asincrono. Il trasmettitore invia pacchetti di bit, come descritto nella figura seguente:

Un pacchetto è composto da:

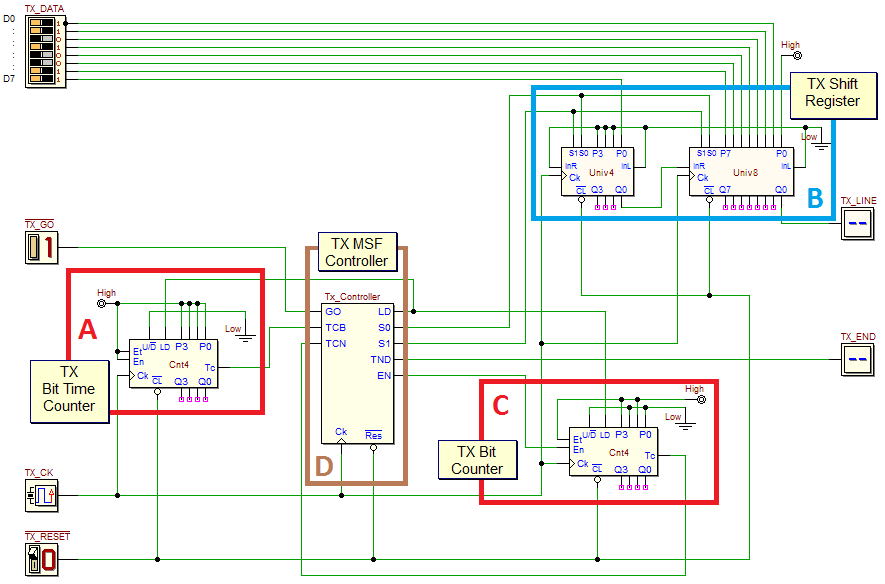

La prossima figura mostra una prima versione del trasmettitore, basata su di una macchina a stati finiti (un click sulla figura aprirà lo schema nell'editor del d-DcS): Il sistema è composto da un contatore del tempo di bit [A, evidenziato in rosso], sulla sinistra della figura, un registro a scorrimento [B, in blu, a destra in alto], un contatore nel numero di bit [C, in rosso, sulla destra], e un controllore [D, in marrone, basato su di una macchina a stati finiti].

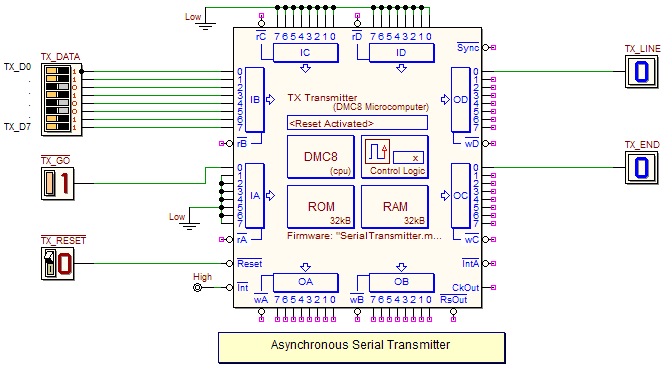

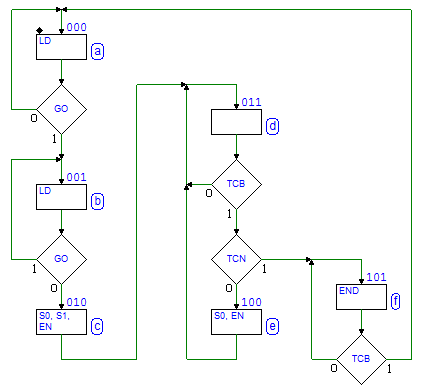

Il comando !TX_GO (GO per la MSF) avvia la trasmissione: i primi due stati (a) e (b) attendono la pressione del pulsante (fornisce un livello "basso" quando è premuto) e, nel frattempo, attivano LD, mantenendo fermi i contatori al valore di predisposizione. Nello stato (c), l'attivazione di S0 e S1 fa caricare il dato parallelo nel registro a scorrimento, mentre EN ordina il decremento del conteggio del numero di bit da trasmettere. Nello stato (d), il controllore attende il segnale TCB dal contatore del tempo di bit: al suo arrivo (ogni 1,6 mS), il controllore attiva (e) lo scorrimento a destra del registro a scorrimento (S1 = '0', S0 = '1') mentre ordina il decremento del numero dei bit da trasmettere (EN = '1'). Quando il numero di bit da trasmettere va a zero (TCN = '1'), il controllore si porta nello stato (f), dove viene generata l'uscita END, per segnalare la fine della trasmissione. Infine, trascorso un ulteriore tempo di bit, il controllore ritorna nello stato (a). Il circuito può essere testato con il simulatore del d-DcS, sia in modalità animazione L'analisi e la simulazione del comportamento del circuito è utile, adesso, per realizzarne una nuova versione, avente le stesse funzionalità, ma basata su di un microcomputer DMC8. Lo schema della nuova versione è visibile nella figura seguente. Un click su di questa aprirà lo schema nel d-DcS. In questo circuito la linea TX_LINE è pilotata dal bit 0 del porto di uscita OD del microcomputer. Il porto IB è connesso alle linee di ingresso TX_DATA, mentre il porto IA, sul bit 0, lege il pulsante !TX_GO. Il porto di uscita OC genera, sul bit 0, il segnale TX_END. Un click aprirà una traccia di una possibile realizzazione del programma in assembly. Una volta terminata la scrittura e il test del programma nel d-McE, potrà essere caricato nella ROM del microcomputer, al fine di simulare la nuova versione del trasmettitore nel d-DcS. Anche in questo caso, una sequenza di test ("TxSequence") è predisposta nella finestra del diagramma temporale. | |||||||||||

Contatore del tempo di bit [A]

Contatore del tempo di bit [A]

che temporale

che temporale  . Una opportuna sequenza di test ("TxSequence") è disponibile nella finestra del diagramma temporale.

. Una opportuna sequenza di test ("TxSequence") è disponibile nella finestra del diagramma temporale.