|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

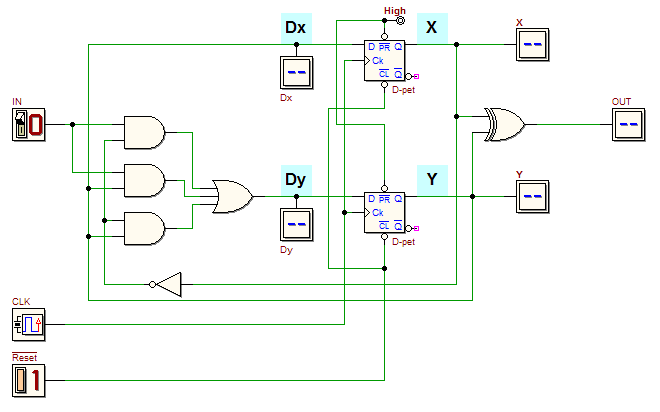

| Si consideri il circuito seguente (un click sulla figura aprirà la rete nel d-DcS): Si analizzi il suo comportamento mediante una simulazione temporale (allo scopo, nel diagramma temporale del d-DcS è predisposta una semplice sequenza di test). Che relazione c'è tra l'ingresso IN e l'uscita OUT? Si consideri questa rete in termini di macchina a stati finiti, e si scrivano le espressioni dello stato successivo e delle uscite, considerando le uscite Q dei due flip-flop come variabili di stato (X e Y, rappresentate in figura). Si compili una Tabella degli Stati, come quella qui rappresentata, corrispondente alle espressioni di cui sopra:

Partendo dalla Tabella degli Stati, si compilino, inoltre, le mappe di Karnaugh dell'uscita OUT e delle variabili Dx e Dy che impongono il prossimo stato X e Y. Si esegua la sintesi delle funzioni booleane rappresentate dalle mappe e si verifichi che corrispondano a quelle ricavate in precedenza. | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||