|

|

||||||||||

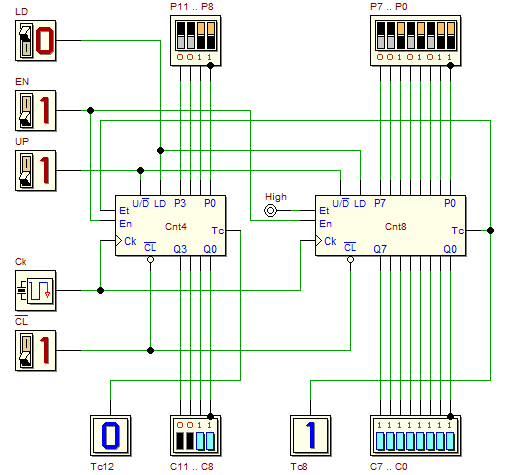

| Questo laboratorio propone l'analisi di un contatore binario da 12 bit, ottenuto utilizzando i componenti Cnt4 e Cnt8, tratti dalla libreria del d-DcS. Dopo l'analisi del funzionamento della rete ottenuta mediante simulazione, si procede alla realizzazione fisica del prototipo su FPGA e alla sua verifica. Con un click sulla figura seguente si aprirà, nel d-DcS, la rete da analizzare: Il componente Cnt4 è un contatore binario sincrono a 4 bit, modulo 16, avanti/indietro, precaricabile. Il Cnt8 presenta la stessa funzionalità, ma è da 8 bit, modulo 256. Nello schema, C11..C0 sono le 12 uscite di conteggio (C11 = MSB, C0 = LSB). L'ingresso di azzeramento !CL è asincrono: quando è attivato (='0'), le uscite C11..C0 sono azzerate, in modo prioritario rispetto agli altri ingressi di controllo, ed indipendentemente dal clock. L'ingresso di precaricamento LD ('Load') è sincrono: quando CL è inattivo e LD è attivo (='1'), gli ingressi P11..P0 sono ricopiati sulle uscite C11..C0 in corrispondenza del fronte di salita dell'ingresso di clock CK (quando LD è attivo, gli altri ingressi della rete EN e UP sono ignorati). L'ingresso di abilitazione EN e di direzione Up sono sincroni. Controllano la modalità di conteggio. Quando !CL e !LD sono inattivi, se EN non è attivo (= '0'), il conteggio è inibito, ma se EN è attivo, ad ogni fronte di salita del clock CK, il valore sulle uscite C11..C0 è incrementato di uno se l'ingresso UP è alto, o decrementato di uno se l'ingresso UP è basso. Il segnale di termine del conteggio (terminal count) Tc12 è attivata dal contatore, per un ciclo di clock, quando le uscite C11..C0 raggiungono il valore massimo ('1111.1111.1111' = 4095), se il conteggio è in avanti. Se il conteggio è all'indietro, Tc12 è attivato quando le uscite C11..C0 raggiungono il minimo valore ('0000.0000.0000'). La rete genera anche il termine del conteggio intermedio Tc8. L'ingresso Et del contatore Cnt8 è sempre attivo, per cui la funzionalità di Tc8 è sempre abilitata, anche quando il conteggio è disabilitato con EN = '0'. Tc8 è collegato all'ingresso Et di Cnt4: ne abilita il conteggio, per un ciclo di clock, solo quando la parte bassa del conteggio, su Cnt8, ha raggiunto il massimo (o minimo) valore (a seconda della direzione di conteggio). Si chiede di verificare il comportamento del contatore,

utilizzando la simulazione per animazione

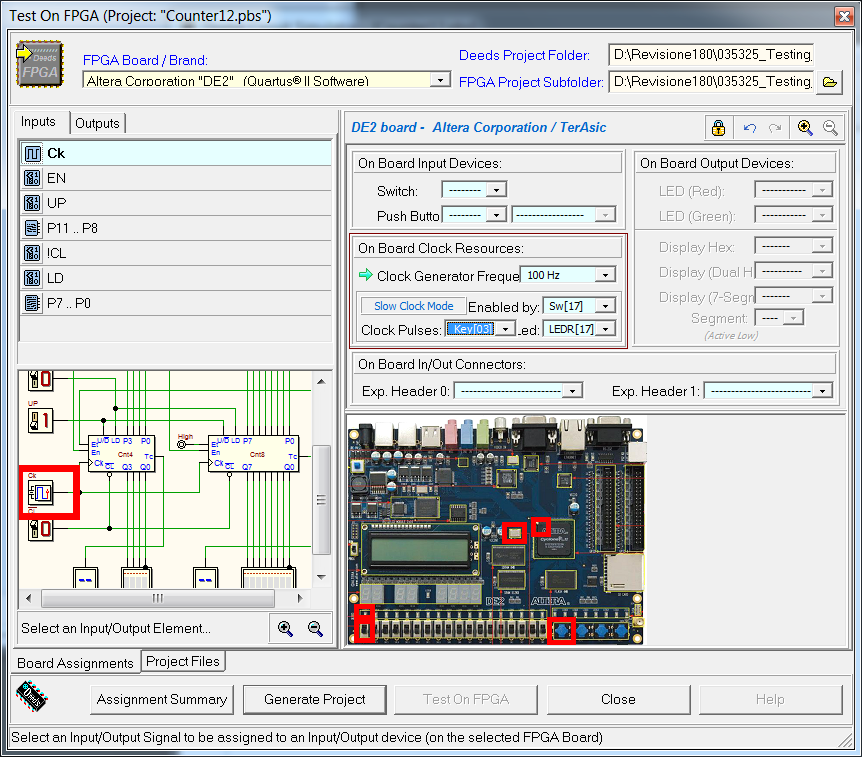

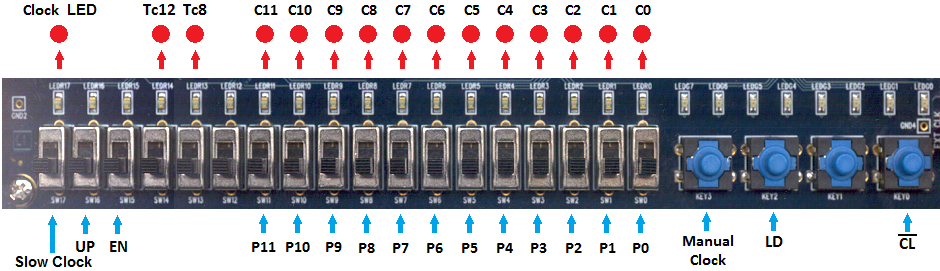

A questo punto inizia la procedura per realizzare fisicamente il contatore sulla scheda FPGA. La procedura generale è descritta passo passo nei tutorial introduttivi: Il comando "Test on FPGA" (del d-DcS) apre la finestra di dialogo visibile qui sot to: Il clock CK è impostato a 100 Hz, una frequenza relativamente bassa, tuttavia sufficiente per l'interazione uomo-macchina. E' stata anche scelta la modalità "Slow Clock Mode": come risulta dai parametri impostati, visibili nella figura, tale modalità è attivabile tramite l'interruttore SW[17]. Lo "Slow Clock" è impostato in modo manuale, comandato dal pulsante Key[03], ed è visualizzato dal led rosso LEDR[17]. In base a questa impostazione, se l'interruttore è a zero, il clock CK lavorerà normalmente a 100 Hz. Se l'interruttore è a uno, il clock sarà generato un impulso alla volta, alla pressione del pulsante Key[03]: potremo esaminare il funzionamento del nostro circuito, con la semplice osservazione visiva. Si noti che la programmabilità della frequenza del clock non è una particolarità della scheda FPGA in uso, ma che è realizzata dal processo di esportazione del progetto, che aggiunge al nostro circuito una rete, basata su contatori, che consente di "scalare" a frequenza bassa il clock a 50 MHz di cui è dotata la scheda. Le associazioni tra schema d-DcS e scheda FPGA, per quanto riguarda gli ingressi e le uscite, sono state già definite nella traccia d-DcS fornita, per cui non è necessario modificarle. Per la comodità dello sperimentatore, le associazioni sono visualizzate anche nella figura seguente, che può essere considerata come il "pannello di controllo" del sistema realizzato, utile per eseguirne il test: Usando gli interruttori e i pulsanti qui sopra indicati, ed osservando l'accensione dei LED, è possibile verificare il funzionamento del sistema. | |||||||||||

e quella temporale

e quella temporale  .

Nella figura seguente suggeriamo una particolare sequenza di test per la simuazione (già definita nella finestra del diagramma temporale), ma può essere molto utile 'esplorare' altre interessanti combinazioni dei segnali di input:

.

Nella figura seguente suggeriamo una particolare sequenza di test per la simuazione (già definita nella finestra del diagramma temporale), ma può essere molto utile 'esplorare' altre interessanti combinazioni dei segnali di input: