|

|

|||||||||||||||

|

Progettare una rete logica che funzioni come porta logica programmabile. La rete ha quattro ingressi A, B, F1, F0, e una uscita P. Questa assumerà il valore delle funzioni NAND, NOR, EXOR di A e B, a seconda della impostazione delle variabili di controllo F1 e F0. La relazione è descritta nella seguente tabella:

Assumendo che la combinazione F1, F0 = 11 non si possa mai presentare, si producano:

Si disegni la rete utilizzando il seguente schema, da completare (un click sulla figura lo aprirà nel d-DcS): Verificare il corretto funzionamento della rete dapprima con la simulazione funzionale , poi

con una simulazione temporale , poi

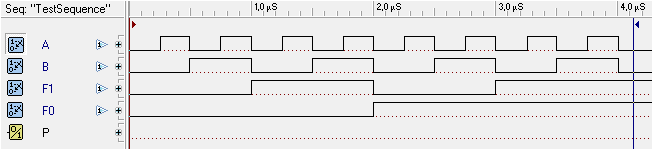

con una simulazione temporale  che ne dimostri il funzionamento. Si suggerisce di utilizzare una sequenza di test come quella proposta nella figura seguente (disponibile nella finestra del diagramma temporale): che ne dimostri il funzionamento. Si suggerisce di utilizzare una sequenza di test come quella proposta nella figura seguente (disponibile nella finestra del diagramma temporale):

| ||||||||||||||||