Progetto di reti combinatorie

2.2 Sintesi AND-OR con uso delle mappe

2.2.5 Mappe a "scacchiera"

Rete corrispondente alla sintesi ricavata dalla mappa:

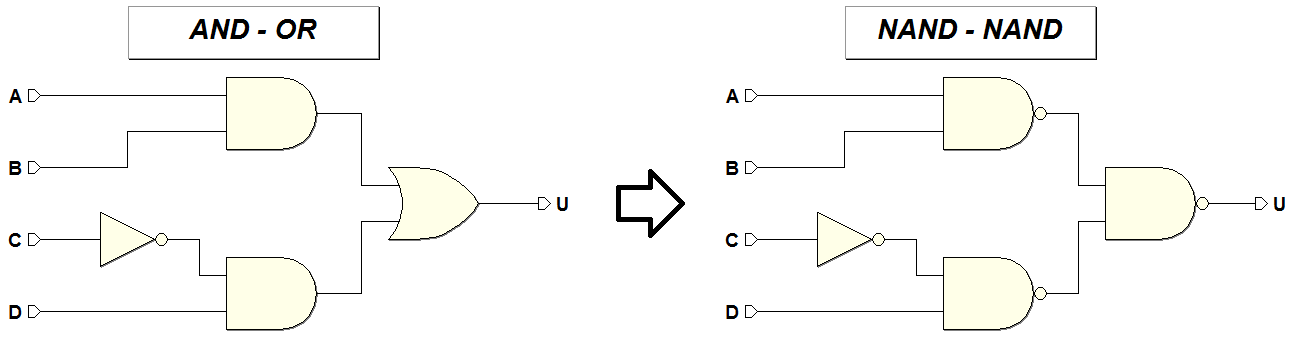

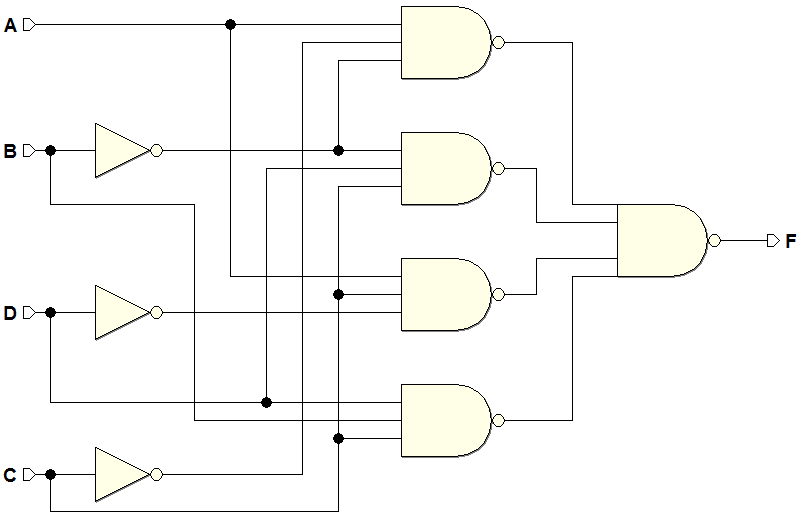

2.4 Sintesi NAND-NAND

Equivalenza e dimostrazione

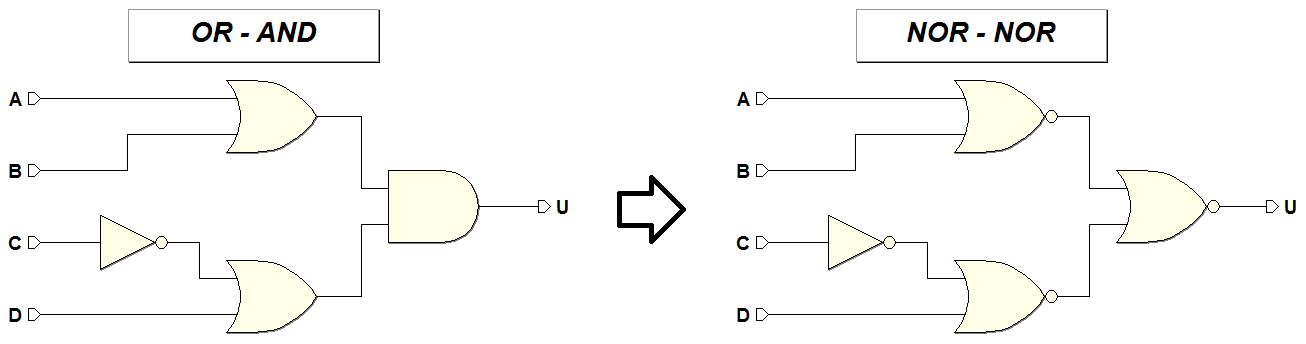

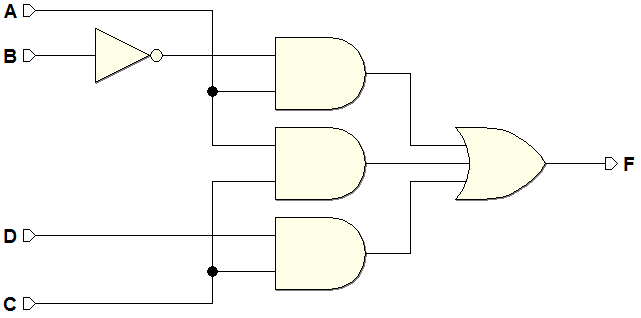

2.5 Sintesi NOR-NOR

Equivalenza

2.6 Reti combinatorie standard

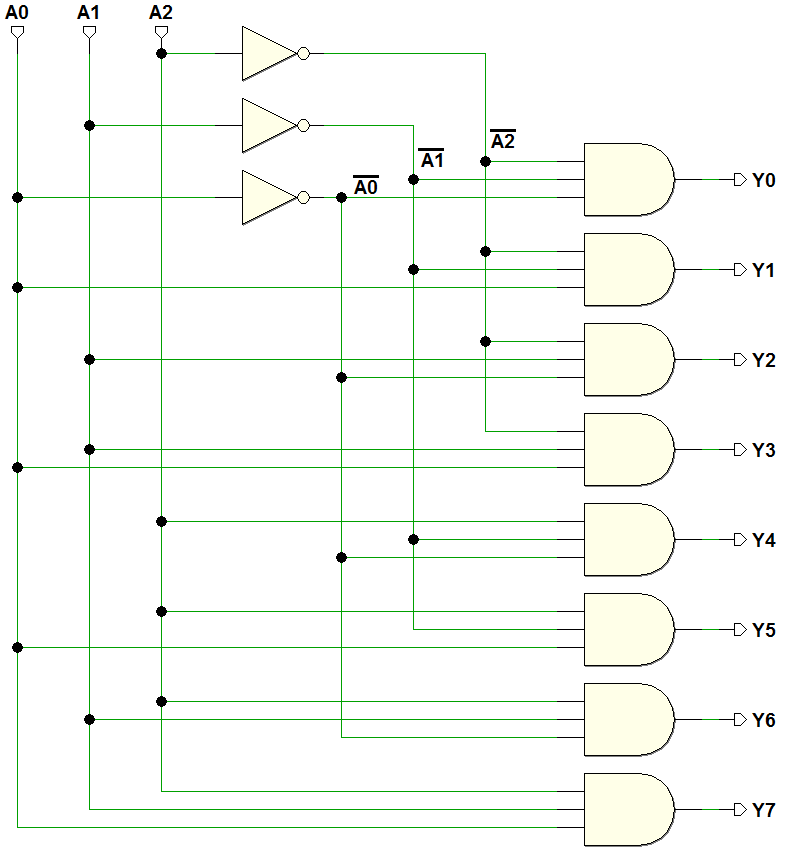

2.6.1 Decodificatore (Decoder)

Sintesi decodificatore 3 - 8

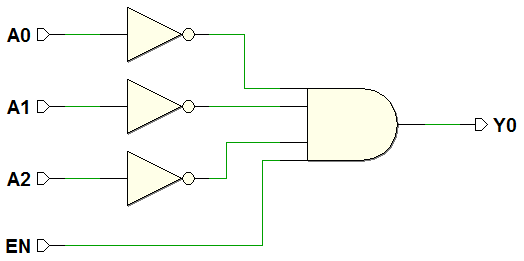

Sintesi uscita Y0 del decodificatore 3 - 8

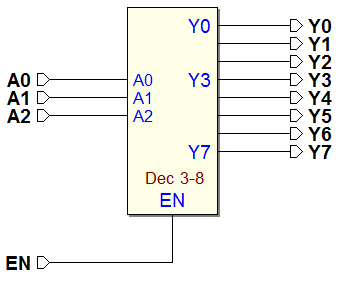

Componente decodificatore 3 - 8 con abilitazione

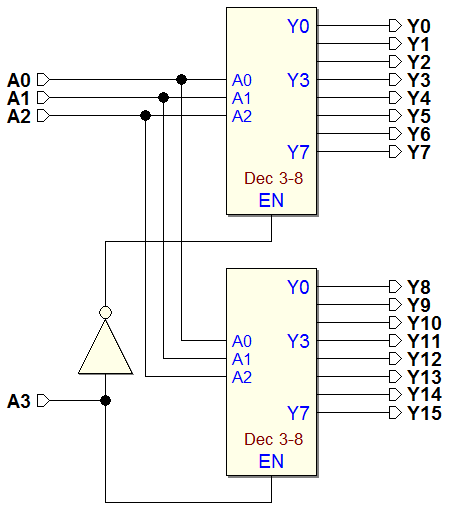

Decodificatore 4 - 16, componendo due decodificatori 3 - 8

2.6.2 Selettore (multiplexer)

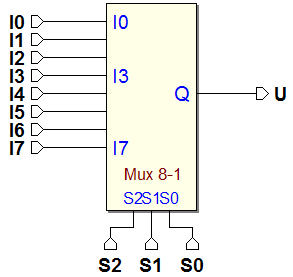

Selettore 8-1

Selettore 8-1: sintesi con decodificatore

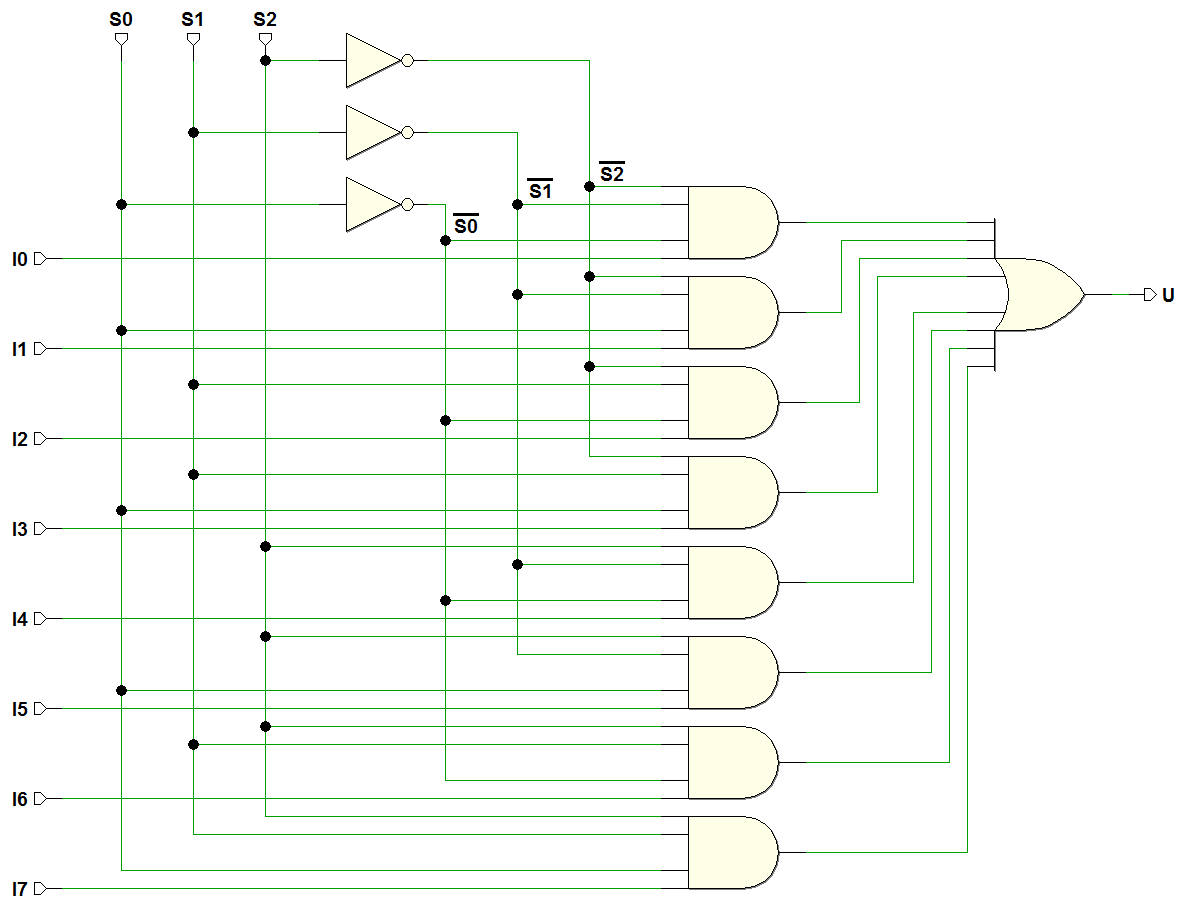

Selettore 8-1: sintesi a due livelli

2.6.3 Deselettore (demultiplexer)

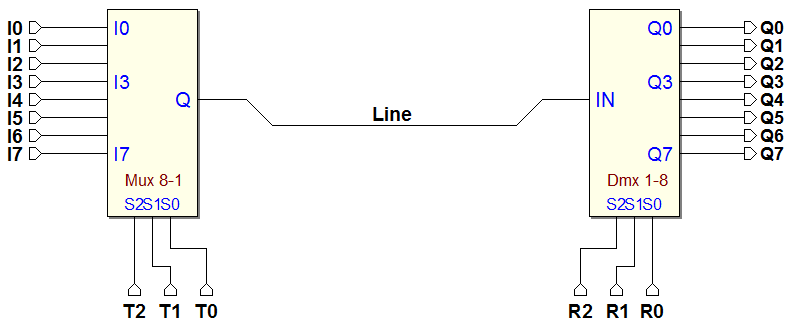

Deselettore 1-8

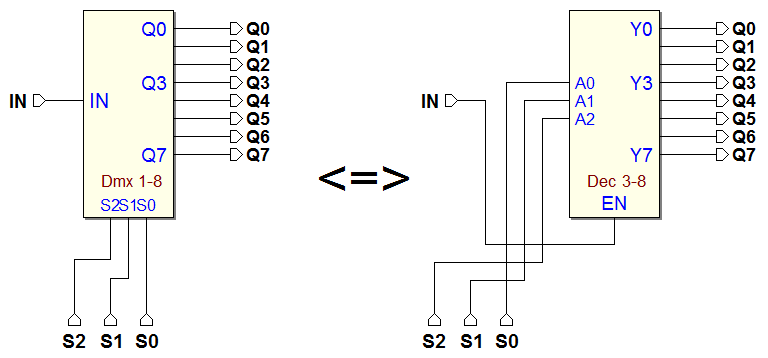

Equivalenza deselettore - decodificatore

Esempio di utilizzo

2.6.6 Uso di selettori per la sintesi di reti combinatorie

Esempio 1

Esempio 2

2.8 Comportamento nel tempo dei circuiti logici

2.8.1 Tempi Caratteristici

Esempio iniziale

Valutazione dei ritardi (solo di trasporto)

2.8.2 Alee

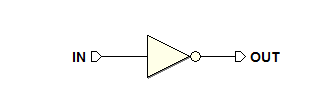

Not, AND

Not, OR

2.8.3 Eliminazione delle alee statiche

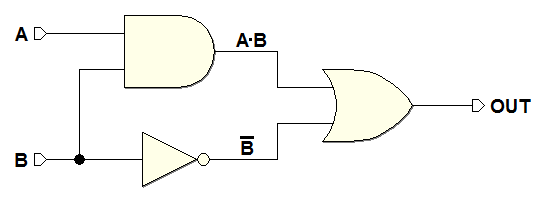

Con alea da eliminare

Alea eliminata

2.9 Esercizi

2.9.2 Alee

Esercizio 2

2.10 Soluzioni

2.10.1 Mappe

Soluzione esercizio 8

2.10.2 Alee

Soluzione esercizio 2

2. Errata Corrige (Cap. 2)

Nessuna