| ||

| Serial transmitter and receiver on FPGA |

|

|

| v1.92 |

In this lab we will design a serial transmitter and receiver system, using two Finite State Machines and a few JK flip-flops. After verification with the simulation, we will implement a physical prototype on FPGA and test it. The system architecture is show in the figure below:

The system is composed by two distinct sub-systems, a transmitter (TX), that drives the serial line SER and a receiver (RX) that receives it. The two subsets are connected by the line SER and share the same clock CK.

Transmitter TX specifications

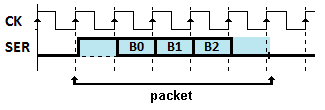

TX gets three bits (B0, B1 and B2), to be transmitted. At every high-to-low transition of the input GO (signal duration is not defined), the TX generates a serial bit packet on the line SER, composed of a START bit at “1”, followed by the sequence of the B0, B1 and B2 bits, and terminated by a STOP bit at “0” (see next figure). Every bit has the duration of a CK clock cycle.

Receiver RX specifications

The receiver RX is build around the RX-FSM and uses three flip-flops JK PET. RX waits for a bit packet on the line SER, and then extracts and conveys in parallel the information bits on the three flip-flop outputs (Q0, Q1 and Q2).

If the STOP bit is received correctly at “0”, the receiver activates the output OK and maintains it active until the assertion of the input ACK (active low) or until a new bit packet will arrive on the line SER. If the STOP bit is received at “1”, the receiver activates the output ERR and keeps it active until the line SER will return to '0'.

A trace of the transmitter ASM chart is available (click on the next figure to open it in the Deeds-FsM). The state variables X,Y, Z and W, the output SER, and the inputs GO, B0, B1 and B2 are already defined

(the  command

allows to verify the FSM setup):

command

allows to verify the FSM setup):

command

allows to verify the FSM setup):

command

allows to verify the FSM setup):

After the design of the two ASM charts, you should verify, using the timing simulation of d-FsM, that the functionality of the FSMs corresponds to specifications.

The FSMs should then be imported as a component on the d-DcS. To that purpose some schematics (to be completed) are available. The first two contain a transmitter-only and a receiver-only schematics: they are useful for verify their stand-alone functionality using timing simulation. The third one represents the complete system, composed of both the transmitter and the receiver, connected by the serial line and sharing the common clock. For each schematic is available, in the timing diagram window, a suitable test sequence.

At this point we begin the procedure for the physical implementation of the project in the FPGA board. The general procedure is described in the introductory tutorials:

Circuit Prototyping on Altera DE2 Board

Circuit Prototyping on Altera DE2 Board

Sequential Circuit Testing on Altera DE2 Board

Sequential Circuit Testing on Altera DE2 Board

To make the project more interesting, we design a a communication systems between two separate DE2 boards, allowing data exchange in both directions: the transmitter on the first board will be connected to the receiver of the second one, and vice versa, with a multi wire cable.

The connection between the boards takes place by means of one of the two 40 pin connectors available in each board. As shown in the figure above, there is a crossed connection transmitter - receiver, in both directions, with 5 wires (GND reference included). Each transmitter clock is connected to to the corresponding receiver, to allow it to sample serial data with the same clock used by the transmitter. Here the schematic of the connection.

The following figure shows wiring that allows preliminary test with only one board, by means of "jumpers" inserted on the connector.

To run the experiments (in both ways, one board or two), we propose a a modified schematic that must be completed with the TX and RX designed by you. The schematic is slightly different from the one used in the simulation phase: a few connections have been modified and a few terminations added: inputs and outputs of the serial signal and other outputs (to wire to LEDs in the board). We recommend to use the schematic supplied, without modifying the input and output terminations, since they contain the information needed for exporting the project on the FPGA board.

When the new modified schematic is completed, you will continue using the "Test on FPGA" comand of the d-DcS (see the following dialog window):

All the needed associations between d-DcS schematic and the FPGA board input/outputs are already set in the given schematic: it is not necessary to modify them.

The clock CK frequency is set to 100 KHz (corresponding to a bit time of 10 microseconds). The "Slow Clock Mode" has also been set: as configured in the figure above, this mode is activable at run time using switch SW[17]. The "Slow Clock" is set to the frequency of 0.5 Hz, and it is displayed by the red LED LEDR[17]. According to this setting, if the switch is set to zero, the clock CK will work at the "normal" frequency of 100 Hz; if the switch is set to one, the clock frequency will be reduced to 0.5 Hz. In this mode, the network functionality can be tested with a simple visual observation.

We suggest a different setting of the Slow Clock mode, for example by assigning to it, instead of the low (0.5 Hz) frequency, a push-button (on the DE2 is still available Key[2]). One press of the push-button produces a single clock pulse, while a continuous pressure generates a succession of pulses. In order to implement that feature it is, obviously, necessary to repeat the project compilation.

Note that the clock programmability feature is not a particularity of the FPGA board, but it is obtained by the design exportation process. This process adds a network to the project, based on counters, that "scales down" the on board 50 MHz clock to the desired low frequency.

As described before, the project uses a few pins of one of the expansion connectors in the board ("GPIO_1") for the outputs of the transmitter TX and the inputs of the receiver RX. To test the system only in a single DE2 board we must insert two jumpers, as highlighted by the yellow arrow in the figure below. With two boards, it is necessary to use the cable already described to attach them together.

Please be careful when placing or removing the jumpers, to avoid mechanical damages. To avoid a very serious risk to destroy the FPGA chip, jumpers must be place and removed only after switching off the board. For the convenience of the experimenter, the associations are highlighted also in the next figure, that can be considered as a "control panel", useful for testing the physical system:

Using the switches and buttons shown above, and observing the status of the LEDs, it is now possible to test the system.