Modifying the propagation times of logic gates

Modifying the propagation times of logic gates

The ability to independently edit the propagation times of each logical gate within a circuit has valuable educational applications, as it effectively demonstrates the impact of delays on network behavior.

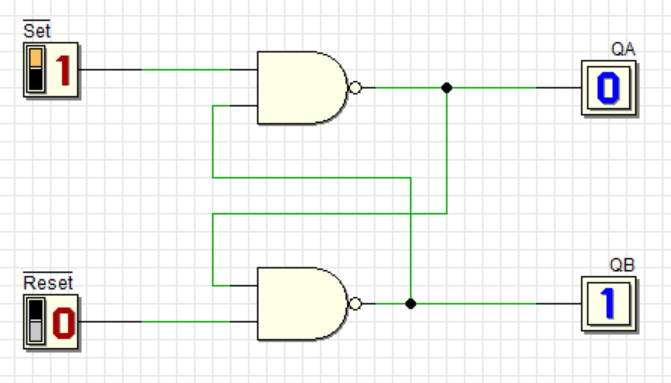

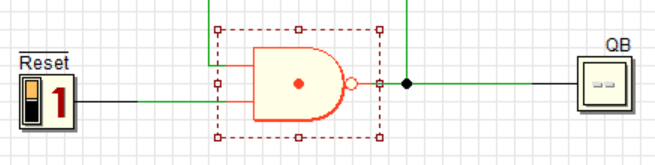

For example, consider the Set-Reset flip-flop shown in the figure below, where the NAND gates have identical propagation times (TpLH = 5 nS, TpHL = 4 nS by default). To open the schematic in Deeds-DcS, click on it.

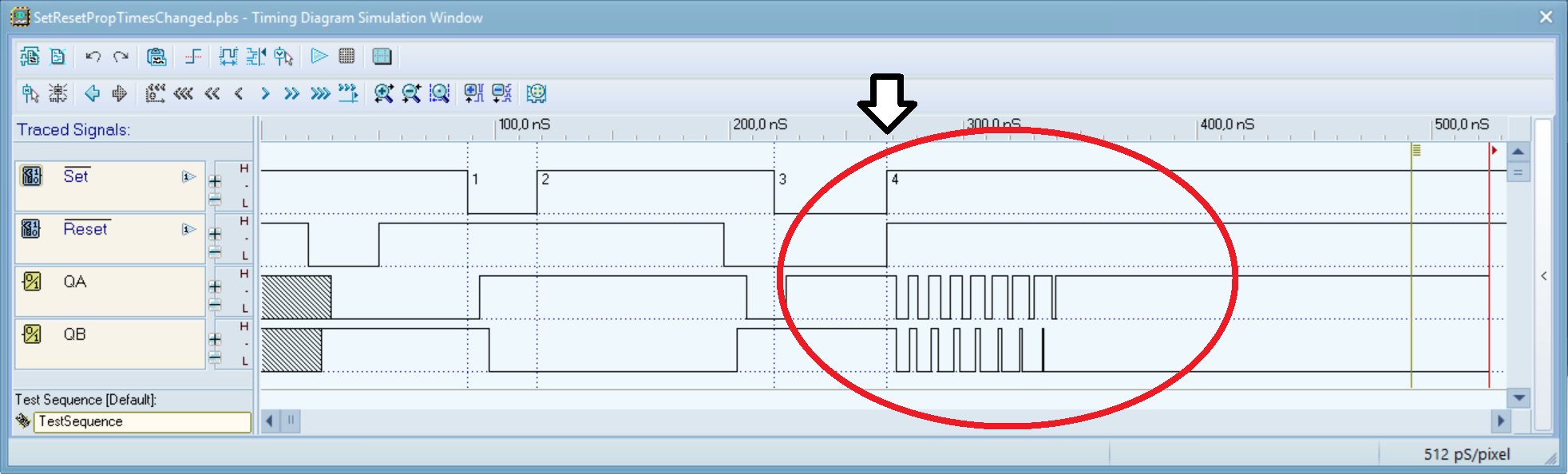

Using the Timing Diagram Window, we will simulate a network where both inputs are simultaneously driven high. In theory, this should create an infinite self-oscillation at the outputs. However, this doesn't occur in reality due to the propagation times being similar, but not identical.

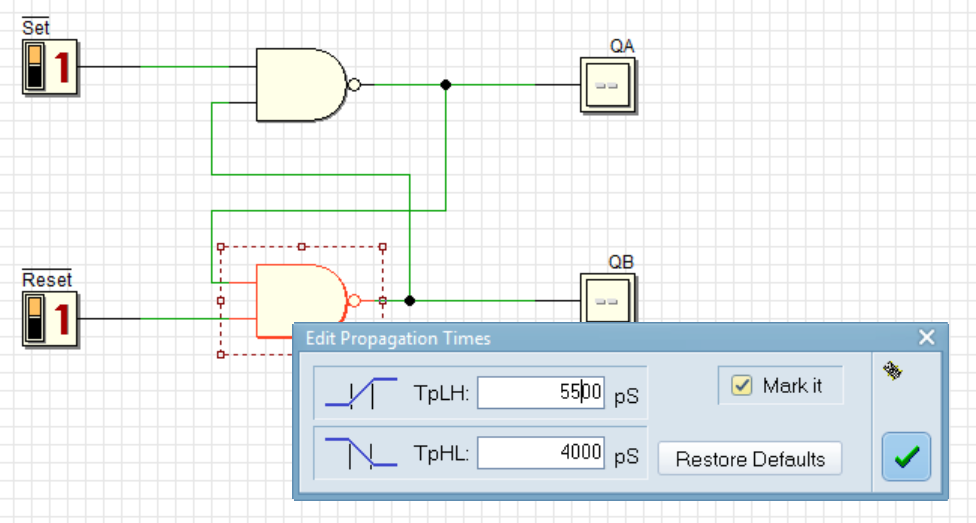

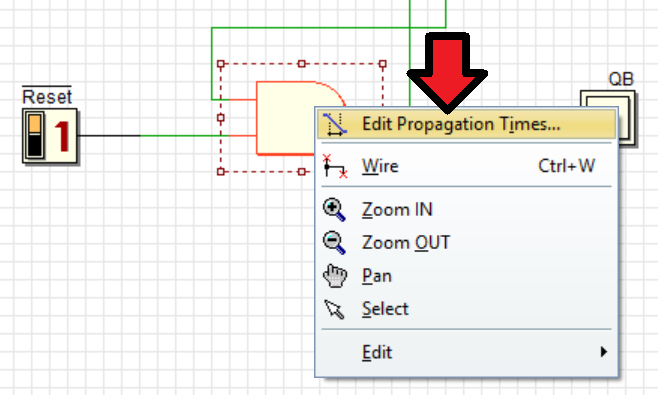

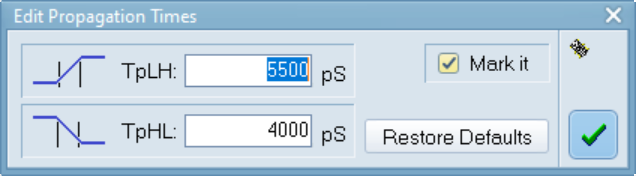

To better reflect real-world scenarios, we need to adjust the timing of the two logic gates to be less symmetrical. To do this, access the component's context menu, as shown in the image below, and choose "Edit Propagation Times."

Double-clicking the component will also open the dialog box adjacent to the logic gate.

The TpLH time has been changed from 5 to 5.5 nS (5500 pS in the screenshot). Ensure that the "Mark it" checkbox is selected. Then, click the OK button. The modified logic gate will be marked with a red dot in its center.

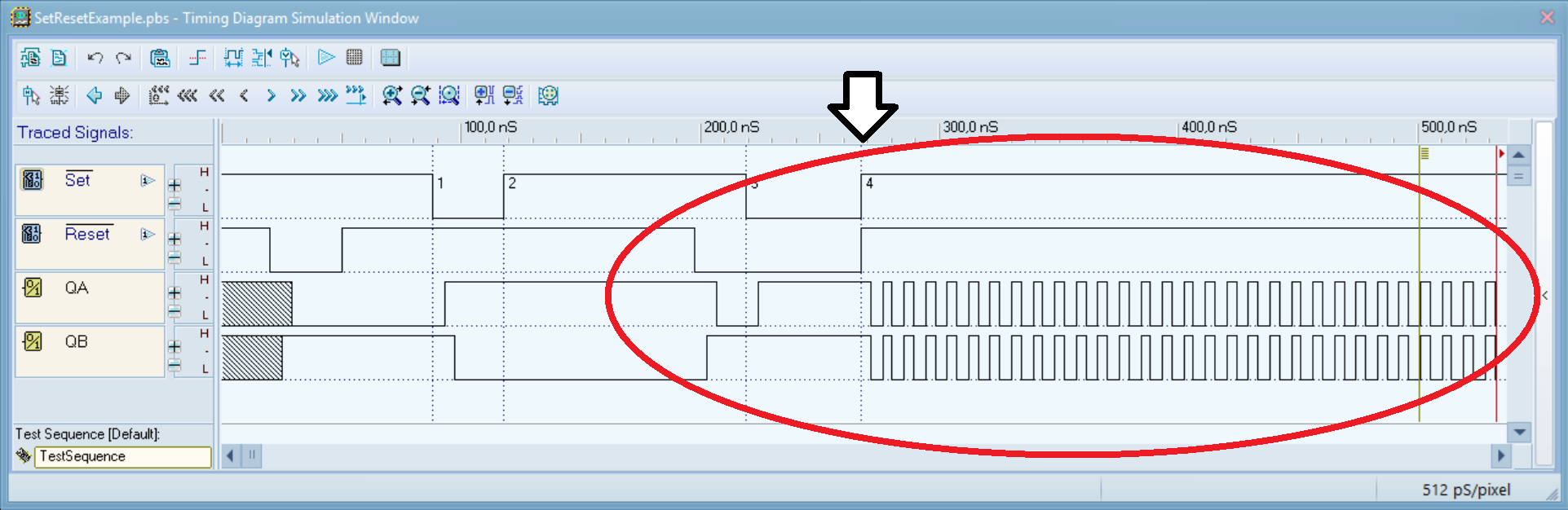

Let's revisit the scenario where both inputs are high simultaneously. The subsequent screenshot displays the outcome.

The self-oscillation will collapse after a few cycles due to the asymmetric delays of the two NANDs.

Available commands

The times can be edited in pS, from a minimum of 2 pS upwards (remember that the simulation time resolution is 1 pS). Please note that for technical reasons it is possible to change the propagation times of all logic gate, except tri-state buffers.

The default propagation times for all logic gates in Deeds are TpHL = 5 ns and TpLH = 4 ns. The "Restore Default" button will reset the times to these default values.

The visibility of the component symbol modification in the schematic diagram can be controlled by the "Mark It" check control, allowing the user to add or remove the marker on the symbol.